# UNIVERSIDAD NACIONAL AUTÓNOMA DE MÉXICO

ESCUELA NACIONAL DE ESTUDIOS PROFESIONALES CAMPUS ARAGÓN

DISEÑO DE UN CIRCUITO DIGITAL PARA ALARMA CON ASISTENCIA TELEFÓNICA IMPLEMENTADO CON EL MICROCONTROLADOR 68HC11

T E S I S

QUE PARA OBTENER EL TÍTULO DE:

INGENIERO MECÁNICO ELECTRICISTA

AREA: INGENIERÍA ELÉCTRICA Y ELECTRÓNICA

JORGE MAURICIO PALACIOS CHÁVEZ

$\mathbf{E}$

N

T

S

$\mathbf{E}$

R

DIRECTOR DE TESIS: ING. ELEAZAR M. PINEDA DÍAZ

MÉXICO,

2005

m342187

UNAM – Dirección General de Bibliotecas Tesis Digitales Restricciones de uso

# DERECHOS RESERVADOS © PROHIBIDA SU REPRODUCCIÓN TOTAL O PARCIAL

Todo el material contenido en esta tesis esta protegido por la Ley Federal del Derecho de Autor (LFDA) de los Estados Unidos Mexicanos (México).

El uso de imágenes, fragmentos de videos, y demás material que sea objeto de protección de los derechos de autor, será exclusivamente para fines educativos e informativos y deberá citar la fuente donde la obtuvo mencionando el autor o autores. Cualquier uso distinto como el lucro, reproducción, edición o modificación, será perseguido y sancionado por el respectivo titular de los Derechos de Autor.

# ESCUELA NACIONAL DE ESTUDIOS PROFESIONALES ARAGÓN

DIRECCIÓN

JORGE MAURICIO PALACIOS CHÁVEZ Presente

Con fundamento en el punto 6 y siguientes, del Reglamento para Exámenes Profesionales en esta Escuela, y toda vez que la documentación presentada por usted reúne los requisitos que establece el precitado Reglamento; me permito comunicarle que ha sido aprobado su tema de tesis y asesor.

TÍTULO:

"DISEÑO DE UN CIRCUITO DIGITAL PARA ALARMA CON ASISTENCIA TELEFÓNICA IMPLEMENTADO CON EL MICROCONTROLADOR 68HC11

ASESOR: Ing. ELEAZAR M. PINEDA DÍAZ.

Aprovecho la ocasión para reiterarle mi distinguida consideración.

A tentamente "POR MI RAZA HABLARÁ EL ESPÍRITU"

San Juan de Aragón, México, 21 de abril de 2003.

LA DIRECTORA

ARQ. LILIA TURCOTT GONZÁLEZ

GB\_

C p Secretaria Académica

C p Jefatura de Carrera de Ingeniería Mecánica Eléctrica

C p Asesor de Tesis

LTG/AIR/lla

## Agradecimientos:

#### A mis revisores:

Ing. Eleazar Margarito Pineda Díaz

Ing. Arturo Ocampo Álvarez

Ing. Martín Hernández Hernández

Ing. Francisco Raúl Ortiz González

Ing. Adrián Paredes Romero

Al Ing. Miguel Ángel Zapata Ferrer (q.e.p.d), por ser más que un amigo.

A Victoria por todas tus enseñanzas, tu amor, tu paciencia, tu comprensión y estar en todos los momentos conmigo.

A Osvaldo, Carlos, René por su amistad.

A todos los que han hecho posible que haya llegado hasta este momento.

A la Universidad Nacional Autónoma de México

" Por mi raza hablará el espíritu"

José Vasconcelos

# **TEMARIO**

| INTRODUCCIÓN                                                                                                                                                                                                                                                                                                                                                               | 2                                           |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|--|--|--|--|

| CAPÍTULO I. DESCRIPCIÓN DEL MICROCONTROLADOR<br>68HC11                                                                                                                                                                                                                                                                                                                     | 4                                           |  |  |  |  |  |

| <ul> <li>1.1 Antecedentes</li> <li>1.2 Descripción</li> <li>1.3 Valores del Fabricante</li> <li>1.4 Diagrama esquemático</li> <li>1.5 Función de los pines</li> <li>1.6 Instrucciones para las entradas y salidas</li> <li>1.7 Instrucciones para la lectura y escritura</li> <li>1.8 Instrucciones de control</li> </ul>                                                  | 4<br>10<br>16<br>21<br>23<br>31<br>33<br>36 |  |  |  |  |  |

| CAPÍTULO II. DISEÑO DEL CIRCUITO DIGITAL                                                                                                                                                                                                                                                                                                                                   | 39                                          |  |  |  |  |  |

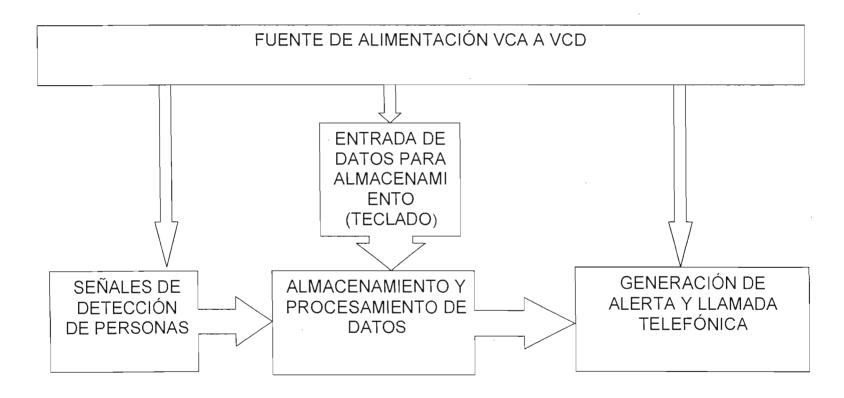

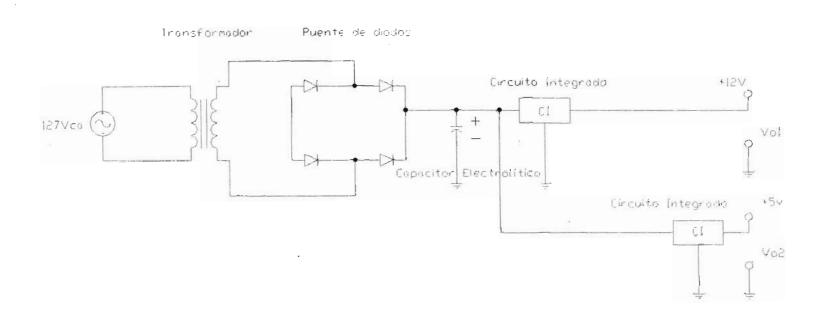

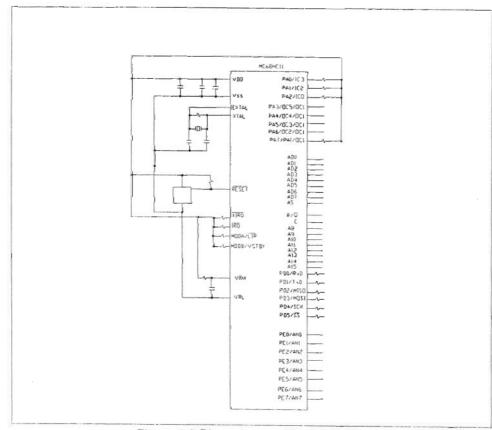

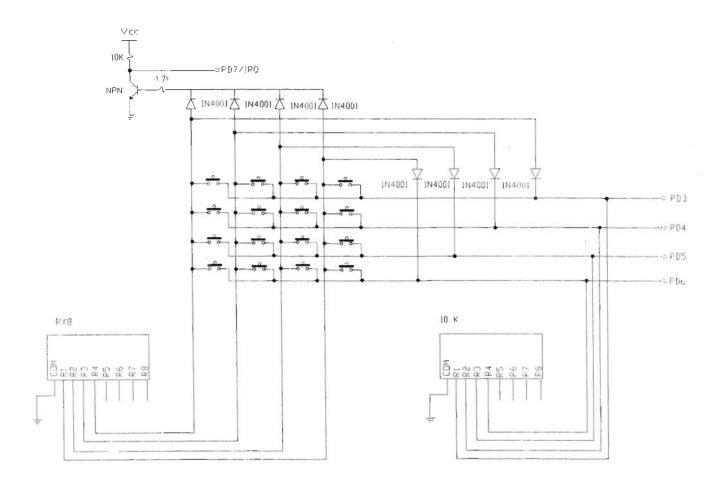

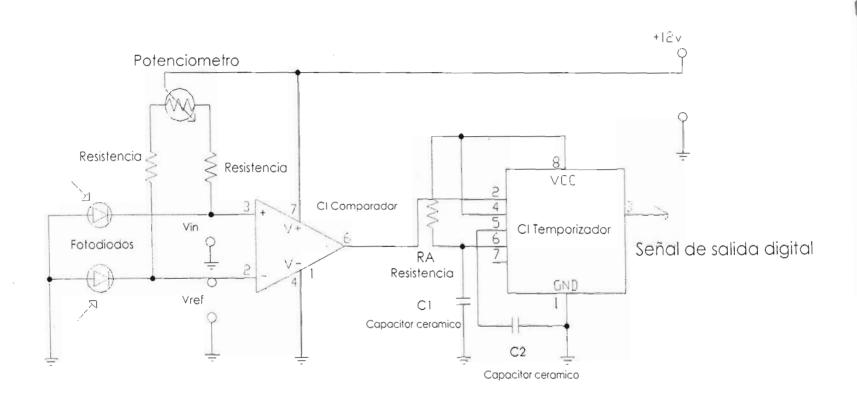

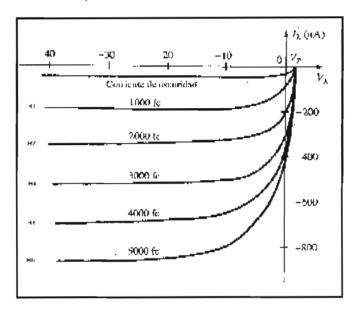

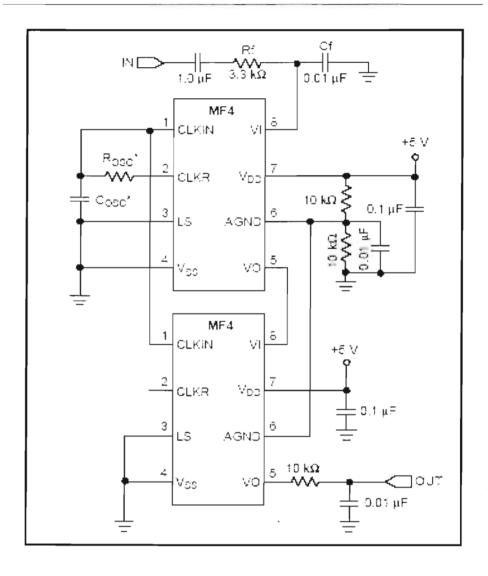

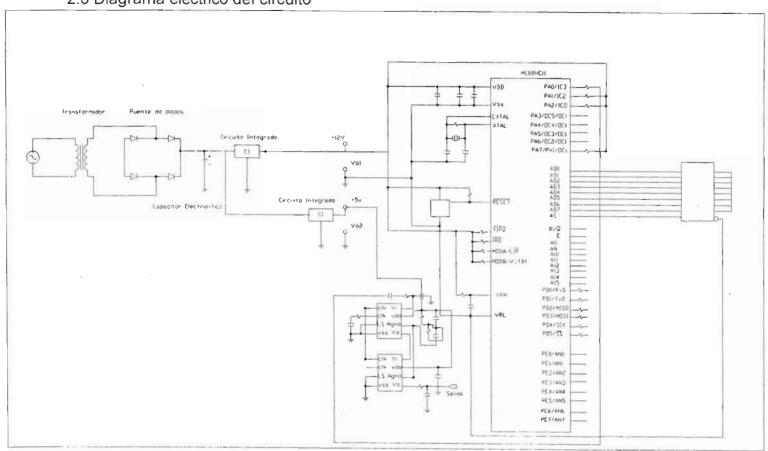

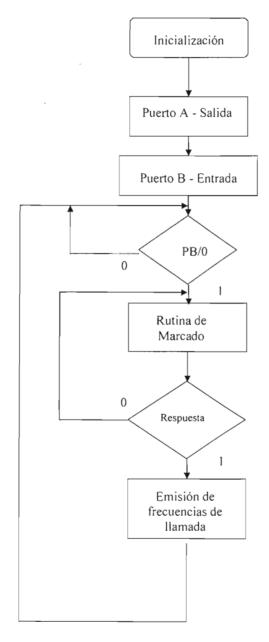

| <ul> <li>2.1 Introducción</li> <li>2.2 Diagrama a bloques</li> <li>2.3 Modulo de Alimentación</li> <li>2.4 Modulo de Almacenamiento y procesamiento de datos</li> <li>2.5 Modulo de Entrada de datos</li> <li>2.6 Modulo de detección de personas</li> <li>2.7 Modulo de generación de alerta y llamada telefónica</li> <li>2.8 Diagrama eléctrico del circuito</li> </ul> |                                             |  |  |  |  |  |

| CAPÍTULO III. PROGRAMACIÓN DEL MICROCONTROLADOR                                                                                                                                                                                                                                                                                                                            | 61                                          |  |  |  |  |  |

| 3.1 Introducción 3.2 Requerimientos 3.3 Lista de programa 3.4 Programación                                                                                                                                                                                                                                                                                                 | 61<br>63<br>64<br>73                        |  |  |  |  |  |

| CONCLUSIONES                                                                                                                                                                                                                                                                                                                                                               | 74                                          |  |  |  |  |  |

| BIBLIOGRAFÍA.                                                                                                                                                                                                                                                                                                                                                              | 75                                          |  |  |  |  |  |

## INTRODUCCIÓN

La necesidad de proteger los bienes materiales, así como la vida, han provocado el desarrollo de sistemas de alerta (alarmas) para prevenir la intrusión de ladrones, asaltantes, o terroristas, a un bien, a un área restringida, o un país.

Las alarmas han evolucionado conforme a las necesidades que se van presentando y también con el fin de ir un paso delante de las personas que se dedican a desactivar las alarmas. Las alarmas se han vuelto después de los ataques en los E.U. en parte importante de inversión en las empresas, ya que las políticas internacionales se han modificado de tal forma que las empresas exportadoras como PEMEX (Petróleos Mexicanos) o empresas en donde la energía es muy importante para una nación como CFE (Comisión Federal de Electricidad) ahora requieren de un sistema de protección (alarma) para proteger de un ataque sobre todo terrorista.

Las alarmas o sistemas de protección van desde un sensor infrarrojo con una sirena donde el sensor detecta y acciona la sirena para saber que hay una presencia humana o mayor a 30 Kg., hasta sistemas mucho más complejo que van desde sistemas de protección perimetral con sensores de fibra óptica, sensores de campos magnéticos conectados en red a sensores magnéticos, infrarrojos, biométricos, de humo, tarjetas magnéticas, circuito cerrado de televisión etc., lo cual hace que esa nueva necesidad de protección se deba de contar con sistemas completos y eficientes; los equipos con estas características serán los que rápidamente se colocaran en el mercado.

Los microcontroladores han hecho de las alarmas sistemas más completos, eficientes y con un bajo costo, en donde desde la aparición de los microcontroladores se puede decir que las alarmas comenzaron a tomar forma y formar parte de la vida cotidiana de las personas.

Objetivo General: Detectar la intrusión a un área restringida y notificar a través de una señal digital y una llamada telefónica la existencia de una intrusión implementada con un microcontrolador 68HC11.

#### Objetivos particulares:

- 1- Mostrar las características funcionales del microcontrolador 68HC11

- 2- Listar las instrucciones de programación que utiliza este microcontrolador.

- 3- Diseñar un circuito digital con las siguientes características:

- a) Capacidad para detectar la presencia de personas

- b) Que se pueda programar y almacenar un No. Telefónico.

- c) La capacidad de hacer llamadas telefónicas.

- d) Que genere un tono de aviso a la persona llamada.

- e) Que corte la llamada después de 30 segundos.

El primer capitulo describe el microcontrolador desde sus antecedentes y sus antecesores. Se encontrará también los valores del fabricante, la descripción de cada uno de los pines y su función de cada uno con los que cuenta el microcontrolador, el diagrama esquemático, y cada una de sus instrucciones para poder controlar las entradas, salidas, escritura y lectura así como las de control, lo cual nos dará un mejor panorama sobre el funcionamiento del microcontrolador.

El segundo capitulo indica el desarrollo el circuito digital, cada una de sus partes son mostradas en el diagrama a bloques, así como el diseño en un diagrama de cada uno de los circuitos que conforman el diseño del circuito digital para alarma. El modulo de alimentación proveerá voltaje a todo el circuito, y el microcontrolador es el modulo de almacenamiento, procesamiento de datos y de entrada de datos. El modulo de detección de personas se constituye de un comparador que como interfaz utiliza fotodiodos, y los capacitores conmutados son los que nos generarán las frecuencias para así generar la llamada al número indicado en el programa y ya teniendo lo anterior se indica el diagrama eléctrico del circuito.

En el tercer capitulo encontraremos, cuales son los comandos e instrucciones que son utilizados para poder realizar las ordenes que el programador le indica a través del programa que se grabará de forma directa desde la computadora al microcontrolador, así como las forma en como se programa y los requerimientos para su programación.

## CAPÍTULO L DESCRIPCIÓN DEL MICROCONTROLADOR

#### 1.1 Antecedentes

En la historia humana siempre se ha necesitado estar "protegido", por ejemplo: lejos de los predadores, de las enfermedades, y de los ladrones. Los ladrones que en nuestra actualidad ya no buscan comida sino objetos de valor monetario, y es a partir de este momento que el ser humano busca formas de protegerse, los cuales sean cada vez más complejos para imposibilitar al ladrón para descifrar la alarma. Las alarmas eléctricas y electrónicas surgen en los años 60, donde se dispone de una tecnología como el transistor que es a un menor costo y mayor eficiencia que el bulbo.

El principio básico de una alarma es un circuito cerrado, el cual al ser interrumpido o abierto este circuito mandará un impulso eléctrico. Pero ahora no es sólo el hecho de enviar un pulso, ahora las alarmas tienen que ser seguras, estables y realizar diferentes funciones para no ser tan vulnerables tanto como los lugares que se protegen, hay alarmas que son activados por Radio Frecuencia (RF), vía telefónica (Dual Tone MultiFrecuency), por biometría (reconocimiento de huellas dactilares), y la más común es por combinación de números (contraseñas), etc. Y fue a finales de los años 80, que comenzaron a surgir las alarmas con alta tecnología, pero fue gracias al surgimiento de los microcontroladores, y a la capacidad en memoria de los mismos, que revoluciono la creación en masa y por consecuencia el bajo costo de las mismas, y aun así siguen siendo inaccesibles para la mayoría de la población.

Para hablar del microcontrolador tenemos que hablar primero del microprocesador Z80 microprocesador de 8 bits, Creado en 1974 por Zilog compatible con Intel. El Z80 era capaz de funcionar a 2,5MHz, siendo uno de sus hermanos mayores, el Z80A, el más usado de la época, ya que alcanzaba los 4MHz. Existiendo el Z80, Z80A, Z80B, Z80H y otros. Podía usar hasta 64k de memoria, algo que suena tal vez ridículo hoy en día, pero que en aquella época sólo estaba reservado a las máquinas más potentes. Entre sus 158 instrucciones figuraban las 78 del 8080, por lo que la compatibilidad era total. Incorporaba más registros de trabajo interno y, al igual que todos los microprocesadores de 8 bits, carecía de la instrucción de multiplicación. Pero no todos, pues el 6809 de Motorola la incluyó años después. Por desgracia, llegó tarde a la arena de los 8 bits y su contribución fue más modesta de lo que merecía. Durante la edad de oro de los 8 bits, más del 80% de los ordenadores usaban o bien el Z80 o bien el 6502 o alguna de sus variantes. El resto se lo repartían el 6809 y otros, 8088, 80186 etc. de Intel, que es muy eficaz en realizar tareas especificas

En el año1974 suceden muchas cosas. Intel saca al mercado el 8080, Zilog el Z80 y un señor llamado Gary Kildall crea el primer sistema operativo transportable para estas maquinas binarias: el CP/M (posteriormente, funda Digital Research, principal competidor de Microsoft en los 80 y los 90 en el terreno de los sistemas operativos). El microprocesador, cerebro de los ordenadores de pequeño tamaño,

aún es caro, por lo que las máquinas que se fabrican tienen poca memoria (también es cara, pero aunque con poca memoria se puede hacer poco, sin microprocesador no se puede hacer nada .)

Durante 2 años, un equipo de desarrolladores proyecta un ordenador para montar en *kit*: el Altair. Usando un 8080 de Intel (el cual se creó para controlar semáforos, pero se hizo famoso por incorporarle el Altair), vio la luz en 1975. La memoria del Altair: 256 octetos.

En 1976, Tandy saca al mercado el TRS-80, con un Z80 y 4k de memoria. Compacto y con posibilidad de ampliación, tuvo bastante éxito en su país de origen, EU.

Llega 1977 y con él, el Apple II. Sucesor del Apple I, fue el primero que se fabricó en serie para un público no necesariamente técnico (aunque la mayoría de sus usuarios lo son). Llevaba un 6502 y 4k de memoria. Entre las muchas tarjetas de ampliación disponibles, estaba la de Z80 para ser usada por CP/M. Este ordenador y sus sucesores usaron el 6502 y sus variantes, llegando hasta 1986, año en el que Apple decidió acabar para siempre con esta línea de ordenadores que le hacía la competencia a su nuevo producto: el Macintosh. El éxito de su línea anterior se plasma en montones de copias piratas en su mayoría fabricadas en Taiwan. Dicho ordenador se muestra en la figura 1.1.

Figura 1.1 el ordenador APPLE II

La preferencia de usar el Z80 en vez del 8080 para CP/M o como procesador principal tenía varios motivos. En primer lugar, el Z80 podía ir más rápido que su competidor. En segundo lugar, sólo necesitaba una tensión de alimentación y no 3 (inconveniente común con algunos tipos de memorias dinámicas de la época, posteriormente superado). En tercer lugar, es probable que fuera más barato. Intel arregló algunos de estos problemas en su versión mejorada, el 8085, pero el Z80 ya se había distanciado mucho.

Ya en 1981, en este año 2 ordenadores significativos salen dispuestos a repartirse el mercado en áreas muy distintas y con características técnicas y precios muy diferentes: el ZX81 de Sinclair y el Osborne 1. El primero tiene un Z80A a 3'5MHz y 1k de memoria, una carcaza negra muy pequeña, un teclado plano de membrana que lo caracteriza, conectándose a un televisor doméstico para

visualizar el funcionamiento y a un cassette para almacenar programas y datos. El segundo tiene un Z80A a 4MHz, 64k de memoria, un monitor de 5 pulgadas de fósforo blanco y 2 unidades de disco flexible de 5 1/4 pulgadas y una capacidad de 90k, todo en una maleta que permite transportarlo a cualquier sitio. El precio en diferencia para el ZX81 de un 16.40 % menor que el Osborne 1. De 1981, recuerden que IBM comienza a vender su PC a precios no aptos para todos los bolsillos. Con un 8088 a 4,77MHz y 64k de memoria, los cuales aparecen en la figura 1.2.

Figura 1.2 el ordenador e impresora Sinclair ZX81 y ZX

Regresemos al ZX81/Osborne1. Observando ambos vemos que el mismo Z80 con el que comenzamos formar parte de una máquina considerada por muchos como un juguete y de un ordenador orientado a un público profesional (especialmente periodistas y profesionales liberales al incorporar CP/M y WordStar, el más famoso procesador de textos de la época). Estos se muestran en la figura 1.3.

Figura 1.3 el ordenador Sinclair ZX Spectrum y ZX Microdrive

La saga del Sinclair ZX Spectrum, nacido en 1982, una de las más legendarias y carismáticas, surgió a raíz de un concurso de la BBC, que ganó Acorn. La mayoría de los ordenadores de los que más se oye hablar (Apple, Atari, Commodore y ahora también Acorn/BBC) usan el 6502. El Z80 lo usan Sinclair y algunos fabricantes que lanzan 1 modelo o 2 y luego no se sabe nada de ellos en el terreno de los microordenadores educativos (de los cuales, por sus cualidades únicas se destaca al Jupiter Ace, que incorpora el lenguaje Forth en lugar de un dialecto del BASIC y aparece en la figura 1.4).

Figura 1.4 Júpiter Ace

En lo profesional, Kaypro, Bondwell y otros tienen ya desde hace años ordenadores similares en características al Osborne, pero de sobremesa, con mucho éxito. Sin embargo, es un hecho que para 1983 la mayoría de usuarios profesionales comienza a mirar hacia los 16 bits a la hora de adquirir un ordenador: Sinclair QL, Apricot F1, IBM PC, Olivetti M20 y Apple Lisa (sucedido por el Macintosh) son algunos de los nombres que comienzan a sonar. En la figura 1.5 se muestra al ordenador sinclair 1.5

Figura 1.5 Sinclair QL

Pero los partidarios del Z80 no se quedan atrás y Spectravideo saca al mercado 2 modelos (el 318 y el 328) que lo incorporan y que forman la base de la norma MSX: muchos fabricantes japoneses (incluyendo a Sony, Mitsubishi, Yamaha, Yashica, etc) y algunos no tan japoneses (Philips y Spectravideo) se ponen de acuerdo para fabricar ordenadores compatibles entre sí en todos los sentidos. 1983 es el año. El venerable Z80 se rejuvenece una vez más al acoplarle circuitería capaz de manejar más de 64k de memoria (teóricamente hasta 1M). Hablamos de la época en que 64k de memoria costaba unas 15000 pts., es decir, más de 4 veces lo que ahora cuestan 64M y aparece en la figura 1.6.

Figura 1.6 Spectravideo 328

En 1984, Amstrad recoge los restos del gastado mercado del CP/M con su CPC464 más unidad de discos, seguido por el efímero CPC664 y el glorioso CPC6128. Estamos en 1985 y comienza la batalla por los 128k. Todas las casas

se apresuran a tener un modelo con la mágica cantidad de memoria. Sinclair, en colaboración con Investrónica (la importadora española, filial de El Corte Inglés), desarrolla el ZX Spectrum+ 128K. Commodore presenta el 128, con 3 procesadores, uno de los cuales, por supuesto, es un Z80 que aparece en la figura 1.7.

Figura 1.7 Amstrad CPC6128

A partir de aquí, los paladines del Z80 son Sinclair, Amstrad y el pacto MSX. ¡Pero no! En 1984, SEGA crea su primera consola de videojuegos doméstica (la Master System) que también lleva un Z80. Y la siguiente generación (Megadrive) lo lleva por compatibilidad con la anterior. Así mismo, muchas placas de videojuegos de finales de los 70 y hasta más allá de mediados de los 80 llevan también un Z80 mostrado en la figura 1.8.

Figura 1.8 Sony HB55P

Sin embargo un Z80 a unos 4MHz y 8k de memoria, con una resolución de 160x160 en 4 tonos de gris y 2 canales de onda cuadrada para el sonido como el GameBoy de Nintendo. Aunque ahora lo hay en color la consola portátil japonesa lleva vendiéndose desde 1989 y ha colocado en el mercado 125 millones de unidades, todas con las mismas características (la de color es compatible con la otra). No hay en el mundo tantos ordenadores con las características perfectamente uniformadas y definidas. Los cartuchos de juegos tienen hasta 512k ilustrado en la figura 1.9.

Figura 1.9 Nintendo Game Boy

Pero podemos ver un Atari Mega STE indicado en la figura 1.10, con un procesador 68000 de 16 *bits* a 16MHz y 4M de. La historia se vuelve a repetir una y otra vez, pues el R3000, cerebro de la consola de Sony, PlayStation, era anteriormente el procesador principal (de 32 bits) de estaciones de trabajo informáticas (carísimas, por cierto) y ahora ha quedado para la historia.

Figura 1.10 Atari Mega STE

Esta tendencia se vio hace mucho tiempo, por lo que los fabricantes comenzaron a producir lo que se denominan *microcontroladores*, que tienen un procesador, memoria y algunos periféricos (curiosa palabra que se aplica a los dispositivos que facilitan la vida del diseñador de sistemas, y entre los que se incluyen puertos de entrada/salida serie y paralelo, temporizadores, contadores, comparadores, conversores de digital a analógico y de analógico a digital, etc.). Algunos llegan a 20MHz y más, y la mayoría son de 8 *bits*, aunque también se usan de 16 y de 32.

Ya sin darnos cuenta, ya que estas exiguas cualidades son sobradas para dispositivos de cierta inteligencia, como videograbadoras, reproductores de CD, cadenas musicales, relojes, hornos de microondas, etc. Multitud de dispositivos

que podemos encontrar a lo largo del día, sin contar con los típicos de los ordenadores (monitores inteligentes, teclados, ratones, etc).

Quizá el ejemplo más común de sistema con esas características sea el teléfono móvil, por varios el símbolo de nuestro tiempo en lo tecnológico y social, y del uso y abuso que la naturaleza humana acostumbra a hacer de las cosas. Efectivamente, cualquier teléfono de hoy en día usa un microcontrolador con características parecidas a las de un Osborne 1 o ZX Spectrum (a veces incluso más potente) para llevar a cabo sus funciones de gestión de todo el sistema: pantalla, teclado, tarjeta, infrarrojos o comunicaciones serie, control de canales y gestión del tiempo del canal y, por supuesto, el sistema de codificación/decodificación de voz. Casi nada.

Es necesario considerar que el 98% de los procesadores que se fabrican a lo largo del año no van a a parar a PC o portátiles, sino que son microcontroladores o procesadores que se usarán en lo que se denominan sistemas empotrados, es decir, que van metidos en un aparato para cumplir una misión concreta. Y sus características son similares a las de los ordenadores de hace 10 o 15 años.

Entonces a partir de este es que el *microcontrolador* por hacer funciones especificas es que lleva su nombre, y hoy en día su accesibilidad tanto en precio como en programación los hacen una herramienta de uso común.

## 1.2 Descripción:

El microcontrolador es una de las formas más básicas de un sistema de computo y son construidos de los mismos elementos básicos.

En el sentido simple, las computadoras producen un patrón especifico de salidas basado en entradas comunes y en las instrucciones de un programa de computadora.

Como muchas computadoras, los microcontroladores tienen como propósito general ejecutar instrucciones. El comienzo real de un sistema de computo es un programa de instrucciones que es provisto por un programador humano. Este programa instruye a la computadora para ejecutar largas secuencias de acciones muy simples para realizar útiles tareas como lo intentado por el programador.

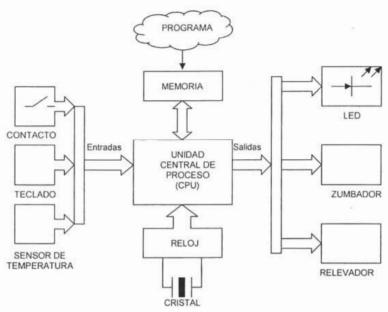

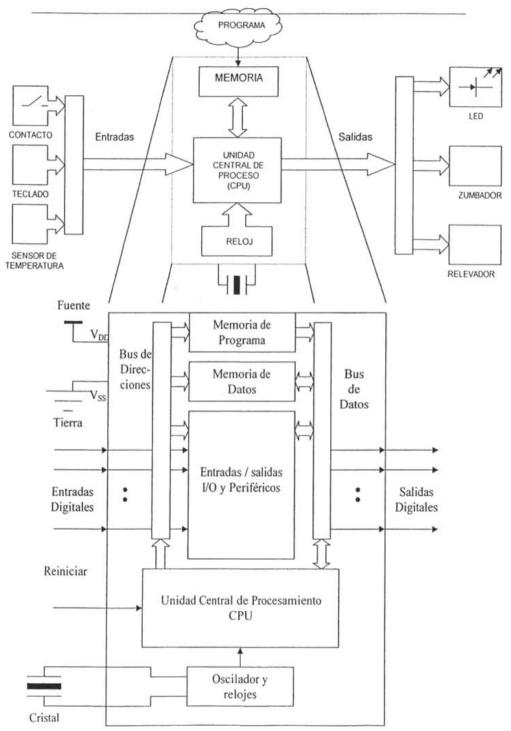

#### Vista completa de un sistema de computadora

La Figura 1.11 muestra una vista de alto nivel de un sistema de computadora. Por cambiar simplemente los tipos de dispositivos de entradas y salidas, esto podría ser una vista de una computadora personal, un espacio medido de una computadora central, o un simple microcontrolador (MCU). Los dispositivos de entrada y salida (I/O) muestran en la figura lo que sucede en un típico dispositivo de I/O basado en un sistema de computadora microcontrolador.

Figura 1.11 Vista completa de un sistema de computadora

#### Entradas del sistema de la computadora

Los dispositivos de entrada proveen información al sistema de la computadora del mundo exterior. En una computadora personal, el dispositivo de entrada más común es el teclado. Los computadores centrales utilizan teclados y en su momento tarjetas perforadas como dispositivos de entrada. El sistema de computo del microcontrolador usualmente utiliza dispositivos simples de entrada como un contacto individual o un pequeño teclado, si bien muchos más exóticos dispositivos de entrada son fundados en muchos sistemas basados del microcontrolador. Un ejemplo de un dispositivo exótico de entrada para un microcontrolador es el censor de oxígeno en un automóvil que mide la eficiencia de combustión para catalizar el vaciado de los gases.

Muchas entradas del microcontrolador pueden sólo procesar señales de entrada digital en los mismos niveles de voltaje como la principal fuente de poder lógica. El nivel 0 o tierra es llamado V<sub>SS</sub> y el positivo (V<sub>DD</sub>) es normalmente 5 Vcd (corriente directa). Un nivel de aproximadamente 0 volts indica una señal *lógica 0* y un voltaje aproximadamente igual al positivo indica una señal *lógica 1*.

El mundo real esta lleno de señales análogas o señales que son algún otro nivel de voltaje. Algunos dispositivos de entrada convierten señales de voltaje de algún otro nivel a niveles de V<sub>DD</sub> y V<sub>SS</sub> necesitados por el microcontrolador. Otro dispositivo de entrada convierte señales *análogas* en señales digitales (valores binarios hechos de 1's y 0's) que la computadora puede entender y manipular.

Algunos microcontroladores hasta incluyen tal circuito convertidor analógico digital en el mismo circuito integrado.

Los *Transductores* pueden ser usados para convertir otra señal del mundo real en señales de nivel lógico que un microcontrolador pueda entender y manipular. Algunos ejemplos incluyen transductores de temperatura, sensores de presión, detectores de nivel de luz, entre otros. Con tal transductor, casi cualquier propiedad física puede ser usada como una entrada al sistema de la computadora.

Salidas del sistema de la computadora.

Dispositivos de salida son usados para comunicar información o acciones del sistema de la computadora al mundo exterior. En una computadora personal, el dispositivo de salida más común es el Tubo de rayos catódicos (TRC) exhibidor. El microcontrolador a menudo utiliza muchos dispositivos simples de salida tal como indicadores individuales, Diodos Emisores de Luz (LED's) o zumbadores (Buzzer).

La traducción de circuitos (algunas veces construidos dentro del mismo circuito integrado como la microcomputadora) pueden convertir señales digitales en señales de niveles de voltaje análogas. Si es necesario , otros circuitos pueden traducir niveles de positivo y negativo Voltaje de corriente directa que son originales de para un MCU en otros niveles de voltaje.

El "controlador en el microcontrolador viene del hecho que estas pequeñas computadoras comúnmente controlan algo como comparar una computadora personal que usualmente procesa información. En el caso de la computadora personal, muchas salidas es información (cualquiera mostrada en una pantalla de TRC o impresión en papel). En contraste, en un microcontrolador, muchas salidas son señales de niveles lógicos que son usadas para controlar al exhibidor (display) LED's o dispositivos eléctricos tales como relevadores o motores.

### Unidad Central de Proceso (CPU)

El CPU es el centro de cada sistema de computo. El trabajo de la CPU es de ejecutar obedientemente el programa de instrucciones que fue provisto por el programador. Un programa de computo instruye al CPU para leer información de entradas, y escribir información para que trabaje la memoria, y para escribir información para salidas. Algún programa de instrucciones involucra decisiones simples que causa el programa, para que cualquiera de las dos continúe con la siguiente instrucción o para saltar un nuevo lugar en el programa.

En la computadora central y la computadora personal, hay una capa actual de programas, comenzando con programas internos ese control son las más básicas operaciones de la computadora. Otras capas incluyen programas de usuario que son cargados en el sistema de la memoria de la computadora cuando ellos están a punto de ser usados. Ésta estructura es muy compleja y no seria un buen ejemplo para mostrar a un principiante como una computadora trabaja.

En un microcontrolador, usualmente sólo un programa es para un trabajo en una aplicación de particular de control. Por ejemplo, el M68HC05 CPU reconoce sólo alrededor de 60 *instrucciones* diferentes, pero estos son representativos de la instrucción de cualquier sistema computarizado. Esta clase de sistema computarizado es un buen modelo para prender las operaciones básicas de la computadora esto es posible porque para conocer que esta sucediendo por cada diminuto paso como el CPU ejecuta un programa.

#### Reloj

Con muy pocas excepciones, los computadores usan un pequeño reloj oscilador para disparar el CPU para mover de un paso de una secuencia a la siguiente. Cada uno de estos pasos en la operación de la computadora toma un ciclo del reloj del CPU.

#### Memoria de la computadora

Varios tipos de memoria de computadora son usados para varios propósitos en el sistema de la computadora. Los principales tipos de memoria establecidos en el microcontrolador son:

- Memoria de sólo lectura (ROM)

- Memoria de escritura y lectura de acceso aleatorio (RAM)

La ROM es principalmente usada para programas y datos permanentes que deben permanecer sin cambiar aun cuando no haya energía aplicada al microcontrolador.

La RAM es usada para almacenar datos temporalmente y cálculos de resultados intermedios durante la operación.

Algunos microcontroladores incluyen otro tipo de memorias, tales como:

- Memoria de sólo lectura borrable programable (EPROM)

- Memoria de sólo lectura eléctricamente borrable programable (EEPROM)

La unidad más pequeña unidad de es un *bit* que puede almacenar un valor de 0 ó 1. Los bits son agrupados dentro de juegos de ocho bits para hacer un *byte*. Muchas computadoras añaden grupos de bits en juegos de 16 o 32 para hacer una unidad a la que se le denomina una *palabra*. El tamaño de una palabra puede ser diferente por distintas computadoras, pero un byte es siempre de ocho bits.

Las computadoras personales trabajan con muy largos programas y grandes cantidades de datos, sólo ellas usan formas especiales de memoria llamados dispositivos de almacenaje en masa (mass storage). El disco flexible, disco duro y el disco compacto son dispositivos de memoria de este tipo. Esto no es inusual para buscar varios millones de bytes de la memoria RAM en una computadora personal. Aunque el almacenaje en masa no es suficiente para guardar los grandes programas y datos usados por las computadoras personales, por lo que la mayoría de las computadoras personales también incluyen disco duro con decenas ó cientos de millones o hasta billones de bytes de capacidad de almacenaje. Un ejemplo: discos compactos, muy similares a aquellos usados grabadores de música popular, tiene una capacidad de alrededor de 600 millones de bytes de memoria de sólo lectura.

### Programa de computadora

La figura 1.12 muestra el programa como una nube porque esto se origina en la imaginación de un programador de computadoras o ingeniero. Esto es comparable a un ingeniero eléctrico pensando en un nuevo circuito o un ingeniero mecánico deduciendo un nuevo juego de piezas. Los componentes de un programa son instrucciones del juego de instrucciones del CPU. Justamente como un proyectista de circuitos puede construir un circuito vibora fuera de simples elementos AND, OR y NOT, un programador puede escribir un programa para agregar números juntos fuera de las simples instrucciones.

Los programas son almacenados en la memoria de una computadora donde ellos pueden ser ejecutados secuencialmente por el CPU.

#### El Microcontrolador

Ahora que se han discutido las varias partes de una computadora, podremos hablar sobre que es un microcontrolador. Un *microcontrolador* puede ser definido como una computadora completa incluyendo al CPU, memoria, un reloj oscilador, e I/O en un solo circuito integrado. Cuando alguno de estos elementos tal como las I/O o memoria están faltando, el circuito integrado sería llamado un *microprocesador*. El CPU en una computadora personal es un microprocesador. El CPU en una computadora central esta compuesta de muchos circuito integrados.

En la parte superior de la Figura 1.12 muestra una computadora genérica con una porción encerrada en una línea punteada. Esa línea es un microcontrolador y en la parte inferior es un diagrama a bloques mostrando esta estructura interna en gran detalle. El cristal no esta contenido dentro del microcontrolador, pero esta

Figura 1.12. Vista Expandida de un microcontrolador

parte es requerida del circuito oscilador. En algunos casos, un componente expansivo menor tal como un resonante cerámico o un circuito resistivo-capacitivo (R-C) puede ser usado en lugar de ese cristal.

#### 1.3 Valores del Fabricante

Descripción general del MC68HC11A8

La alta densidad complementaria del semiconductor metal-oxido (HCMOS) MC68HC11A8 es un avanzado MCU de 8 bit altamente sofisticado, con capacidad periférica en el chip. Nuevas técnicas de diseño son usadas para lograr un bus nominal de velocidad de 2 MHz. En suma, el su diseño completamente estático permite la operación a frecuencias debajo de la corriente directa (cd), además reduciendo el consumo de energía.

La tecnología HCMOS usada en el MC68HC11A8 combina pequeño tamaño y alta velocidad con el baja energía y alta inmunidad al ruido de CMOS. Dentro del sistema del chip incluve:

- 8 Kbytes de memoria de sólo lectura (ROM)

- 512 bytes de memoria programable eléctricamente borrable (EEPROM)

- 256 bytes de memoria de acceso aleatorio (RAM)

Mejores funciones periféricas son provistas en el Chip. Un 8vo canal convertidor analógico – digital (A/D) es incluido con ocho bits de resolución.

Una interfase de comunicación serial asíncrona (SCI) y una interfase periférica serial sincronía separada (SPI) están incluidas.

El principal bit 16, corriendo libre en el sistema temporizado tiene tres líneas de entrada de captura, cinco líneas de salida comparadoras, y una función de interrupción en tiempo real. Un subsistema pulso acumulador de 8 bit puede contar eventos o medir periodos externos.

Es incluido en el Chip un monitoreo en su circuitería para proteger contra errores. Una computadora operando apropiadamente (COP) perro guardián del sistema protege contra fallas del software. Un sistema de reloj monitor genera un sistema de reinicio en caso de que se pierda o corra muy lento. Un código ilegal detectado en el circuito provee una interrupción no enmascarable si un código es detectado.

Dos instrucciones controlan modos de ahorro de energía, WAIT y STOP, son validos para conservar energía adicional. Estos modos hacen a la familia M68HC11 especialmente atractiva para automotivos y aplicaciones de manejo de batería.

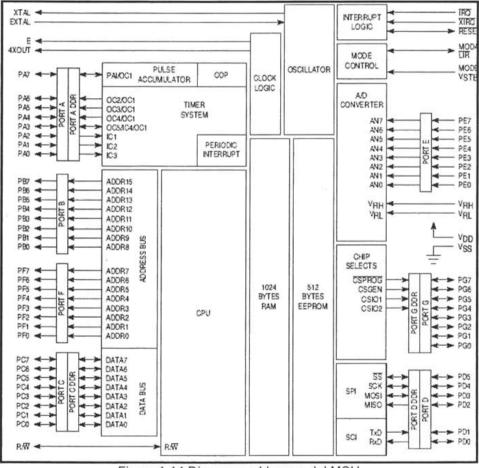

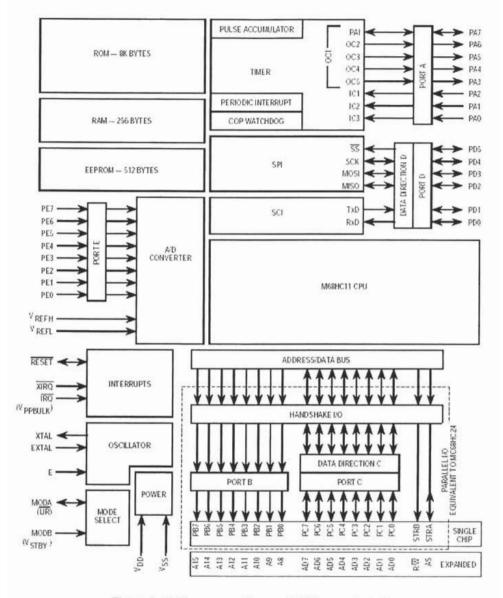

Figura 1.14 es un diagrama a bloques del MCU MC68HC11A8. Este diagrama muestra los subsistemas mayores y cómo se relacionan a los pines del MCU. En la esquina inferior derecha de este diagrama, el subsistema de I/O paralelo se muestra dentro de un cuadro punteado. Las funciones de este subsistema se pierden cuando el MCU se opera en los modos extendidos, pero el puerto MC68HC24 unidad de reemplazo puede usarse para recobrar las funciones que estaban perdidas. Las funciones se restauran de tal forma que el programador del

software es incapaz para decir cualquier diferencia entre un sistema de un únicochip o un sistema extendido que contiene el MC68HC24. Usando un sistema extendido que contiene un MC68HC24 y un EPROM externo, el usuario puede desarrollar software pensado para una aplicación de un único-chip.

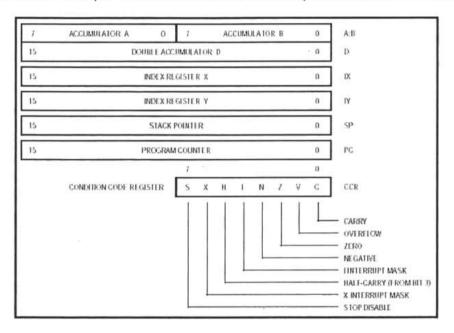

#### El Modelo de programador

Además de ejecutar todos las instrucciones del M6800 y del M6801, el juego de instrucciones del M68HC11 incluye 91 nuevos opcodes. La nomenclatura M68xx se usa junto con una arquitectura de CPU específica y la instrucción puso como opuesto a la nomenclatura de MC68HC11xx que es una referencia a un miembro específico de la Familia de M68HC11 de MCUs.

Figura 1.14 Diagrama a bloques del MCU

La Figura 1.15 muestra los siete registros del CPU disponibles al programador. Los dos acumuladores de 8-bit (A y B) puede usarse por algunas instrucciones cuando un solo acumulador de 16-bit llamado el registro D, que permite un juego de operaciones de 16-bit aunque el CPU es técnicamente un procesador de 8-bit. El grupo más grande de instrucciones agregado involucra al índice de registro Y. Doce instrucciones de manipulación de bits que pueden operar en cualquier memoria o ubicación de registro se agregan. El intercambio D con X e intercambio D con las instrucciones de Y pueden usarse para traer rapidamente el índice de valores dentro del acumulador doble (D) donde la aritmética de 16-bits puede usarse. Dos 16-bit por 16-bits divide las instrucciones que también son incluidas.

Figura 1.15 MC68HC11 Modelo del programador

#### Los Derivados del producto

La Familia M68HC11 de MCU está compuesta por los miembros del producto listado en la tabla 1.1. En la tabla 1.1 y 1.2 se explica cómo los números de parte del producto son construidos.

| Product     | ROM<br>(KBytes) | RAM<br>(Bytes) | EPROM:OTP<br>(KBytes) | EEPROM<br>(Bytes) | Timer <sup>(1)</sup> | Serial      | A:D           | PWM                                   | Operating<br>Voltage<br>(V) | Bus<br>Frequency<br>(Max)<br>(MHz) |

|-------------|-----------------|----------------|-----------------------|-------------------|----------------------|-------------|---------------|---------------------------------------|-----------------------------|------------------------------------|

| MC68HC11D6  | -               | 192            | -                     | =                 | 3:4 IC<br>4/5 OC     | SCI<br>SPI  | -             | -                                     | 3.0, 5.0                    | 3                                  |

| MC68HC11D3  | 4               | 192            | -                     | -                 | 314 IC<br>415 OC     | SCI<br>SPI  | -             | -                                     | 3.0. 5.0                    | 3                                  |

| MC68HC11E0  | 100             | 512            | 2-2                   | -                 | 3/4 IC<br>4/5 OC     | SCI<br>SPI  | 8-CH<br>8-bit | -                                     | 3.0, 5.0                    | 3                                  |

| MC68HC11E1  | -               | 512            | 1-1                   | 512               | 3/4 IC<br>4/5 OC     | SCI<br>SPI  | 8-CH<br>8-tit | -                                     | 3.0, 5.0                    | 3                                  |

| MC68HC11E2  | -               | 256            | -                     | 2048              | 3/4 IC<br>4/5 OC     | SCI<br>SPI  | 8-CH<br>8-bit | -                                     | 5.0                         | 2                                  |

| MC68HC11E9  | 12              | 512            | -                     | 512               | 3/4 IC<br>4/5 OC     | SCI<br>SPI  | 8-CH<br>8-bit | -                                     | 3.0, 5.0                    | 3                                  |

| MC68HC11E20 | 20              | 768            | -                     | 512               | 3/4 IC<br>4/5 OC     | SCI         | 8-CH<br>8-bit | -                                     | 5.0                         | 3                                  |

| MC68HC11F1  | _               | 1              | -                     | 512               | 3/4 IC<br>4/5 OC     | SCI<br>SPI  | 8-CH<br>8-bit | -                                     | 3.0, 5.0                    | 5                                  |

| MC68HC11K0  | -               | 768            | -                     | -                 | 3/4 IC<br>4/5 OC     | SCI<br>SPI  | 8-CH<br>8-bit | 4-CH<br>8-bit<br>or<br>2-CH<br>16-bit | 3.0, 5.0                    | 4                                  |

| MC68HC11K1  | -               | 768            | -                     | 640               | 3/4 IC<br>4/5 OC     | SCI+<br>SPI | 8-CH<br>8-bit | 4-CH<br>8-bit<br>or<br>2-CH<br>16-bit | 3.0. 5.0                    | 4                                  |

| MC68HC11K4  | 24              | 768            | -                     | 640               | 3/4 IC<br>4/5 OC     | SCI+<br>SPI | 8-CH<br>8-bit | 4-CH<br>8-bit<br>or<br>2-CH<br>16-bit | 3.0, 5.0                    | 4                                  |

Tabla 1.1 Familia del HC11

Continua

| Product      | ROM<br>(KBytes) | RAM<br>(Bytes) | EPROMIOTP<br>(KBytes) | EEPROM<br>(Bytes) | Timer <sup>(1)</sup> | Serial               | ΑĐ              | PWM                                   | Operating<br>Voltage<br>(V) | Bus<br>Frequency<br>(Max)<br>(MHz) |

|--------------|-----------------|----------------|-----------------------|-------------------|----------------------|----------------------|-----------------|---------------------------------------|-----------------------------|------------------------------------|

| MC68HC11KS2  | -               | 1              | 32                    | 640               | 3:4 IC<br>4:5 OC     | SCI+<br>SPI          | 8-CH<br>8-bit   | -                                     | 5.0                         | 4                                  |

| MC68HC11KW1  | -               | 768            | -                     | 640               | 3:4 IC<br>4:5 OC     | SCI+<br>SPI          | 10-CH<br>10-bit | 4-CH<br>8-bit<br>or<br>2-CH<br>16-bit | 5.0                         | 4                                  |

| MC68HC11P1   | -               | 1              | -                     | 640               | 3/4 IC<br>4/5 OC     | Triple<br>SCI<br>SPI | 8-CH<br>8-bit   | 4-CH<br>8-bit<br>or<br>2-CH<br>16-bit | 5.0                         | 4                                  |

| MC68HC11P2   | 32              | 1              | -                     | 640               | 3/4 IC<br>4/5 OC     | Triple<br>SCI<br>SPI | 8-CH<br>8-bit   | 4-CH<br>8-bit<br>or<br>2-CH<br>16-bit | 5.0                         | 4                                  |

| MC68HC711D3  | -               | 192            | 4                     | -                 | 3/4 IC<br>4/5 OC     | SCI                  | -               | -                                     | 5.0                         | 3                                  |

| MC68HC711E9  | -               | 512            | 12                    | 512               | 3/4 IC<br>4/5 OC     | SCI                  | 8-CH<br>8-bit   | -                                     | 3.0, 5.0                    | 4                                  |

| MC68HC711E20 | -               | 768            | 20                    | 512               | 3/4 IC<br>4/5 OC     | SCI                  | 8-CH<br>8-bit   | -                                     | 5.0                         | 4                                  |

| MC68HC711KS2 | -               | 1              | 32                    | 640               | 3/4 IC<br>4/5 GC     | SCI+<br>SPI          | 8-CH<br>8-Eit   | -                                     | 5.0                         | 4                                  |

Tabla 1.2 Familia del HC11

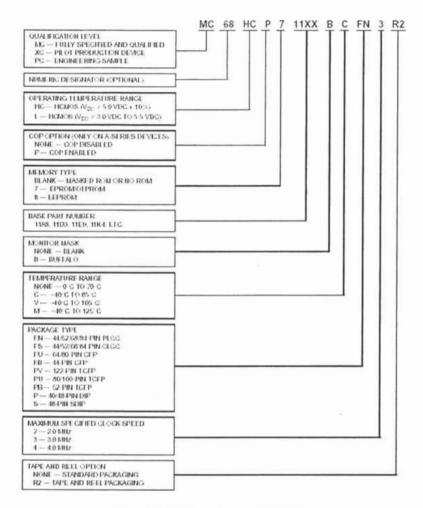

La matricula de estas componentes contiene caracteres alfanuméricos para que el fabricante anote las diferentes características. EN la figura 1.16 aparece la descripción de cada uno de los caracteres del microcontrolador HC11

Todos los M68HC11 incluyen un cronómetro de 16-bits de 8-canales con interrupción de tiempo-real y pulso acumulador. Todos los cronómetros tienen tres entradas de captura, cuatro salidas comparan, y un octavo canal que puede configurarse como una cuarta entrada de la entrada o una quinta salida de comparación.

Figura 1.16 Caracteres del HC11.

# 1.4 Diagrama esquemático

La figura 1.17 muestra los bloques que conforman el funcionamiento del microcontrolador en su modo expandido (ADO – A15), además de que se pueden ver los bloques de memoría en caso de requerir de más capacidad de almacenamiento, y los puertos de entrada y salida.

Figura 1.17 Diagrama a bloques del Microcontrolador

El grupo más grande de instrucciones sumado involucra al registro del índice Y . Doce instrucciones de manipulación de bits que pueden operar en cualquier memoria o se agrega en una locación de registro. El intercambio D con X y el intercambio D con las instrucciones de Y puede ser usada rápidamente tomando los valores del índice dentro del doble acumulador (D) donde 16-pedazo

aritméticos pueden usarse. Dos 16-bits por 16-bits divida las instrucciones también son incluidos.

## 1.5 Funciones de los pines

El Modelo MC68HC11F1 esta disponible sólo en un circuito integrado de 68 pines. El MC68HC11F1 fue el primer direccionador de bus de datos no multiplexado en la familia M68HC11. Este MCU incluye un Kbyte de RAM en el chip y selector de chip inteligente para una simple conexión para un programa de memoria sin la necesidad de cualquier chip lógico externo Y se muestra en la figura 1.18.

Figura 1.18 Diagrama esquemático

#### El Pin VDD y VSS:

La fuente de poder para alimentar al MCU es proveída a través de estos pines.  $V_{DD}$  es la entrada del positivo, y  $V_{SS}$  es tierra (ground). El MCU usa una sola fuente de poder, pero en algunas aplicaciones es opcional como fuente de poder para referencia A/D y /o batería de respaldo de una memoria de acceso aleatoria (RAM). Estas fuentes adicionales son opcionales, y el MCU, incluye RAM y A/D, puede operar con una fuente de 5V (nominal).

#### EI Pin MODB/VSTBY y MODA/LIR:

Pines de selección de modos. El modo B/standby fuente RAM (MODB/V<sub>STBY</sub>) selecciona entre el pin de modo de entrada y el pin de una fuente de poder standby. El pin de modo de instrucción de registro A/load (MODA/LIR)es usado

para seccionar el modo de operación del MCU cuando el MCU esta en restablecimiento (reset), y esta operando como una señal de salida de diagnóstico cuando el MCU esta ejecutando instrucciones.

El modo hardware selecciona mecanismos de inicio con los niveles lógicos de los pines MODA y MODB cuando el MCU esta en estado de reset. El modo A selecciona entre el modo de un solo chip y modo expandido; mientras que el modo B selecciona entre la variación normal y la variación especial del modo de operación escogida.

| Inputs |      | Mada Basashilas    | Control Bits in HPRIO (Latched at Reset) |      |     |     |  |  |  |  |

|--------|------|--------------------|------------------------------------------|------|-----|-----|--|--|--|--|

| MODB   | MODA | Mode Description   | RBOOT                                    | SMOD | MDA | IRV |  |  |  |  |

| 1      | 0    | Normal single chip | 0                                        | 0    | 0   | 0   |  |  |  |  |

| 1      | 1    | Normal expanded    | 0                                        | 0    | 1   | 0   |  |  |  |  |

| 0      | 0    | Special bootstrap  | 1                                        | 1    | 0   | 1   |  |  |  |  |

| 0      | 1    | Special test       | 0                                        | 1    | 1   | 1   |  |  |  |  |

Tabla 1.3 Modo selección de hardware.

El pin modo A sirve de función alternante de carga de instrucción de registro (Siglas en inglés LIR) cuando el MCU no esta en reset. La salida abierto-drenado activo-bajo LIR manda bajo cuando el primer E ciclo de cada instrucción. El pin modo B sirve de función alternante de una fuente de poder standby (V<sub>STBY</sub>) para mantener los contenidos de RAM cuando V<sub>DD</sub> no esta presente.

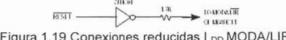

Durante la ejecución del programa, en el pin pasa un nivel lógico bajo durante el primer ciclo da cada instrucción por la señal LIR y es levantada entre señales LIR a través de la resistencia externa 4.7 KΩ.

\*En sistema de modo expandido, la resistencia de 4,7 kΩ es importante para minimizar la fuente de corriente, lógico deberá ser usado para mandar por el pin MODA/LIR, lo que resulta mejor que solo usar un simple nivel lógico alto (ver fig. 1.19)

Durante el restablecimiento, el pin MODA se manejaría alto para seleccionar el modo extendido. Después de que se restablezca, los pines LIR se manejarían bajos por la lógica. La lógica no debe ser operada contra una detención pullup, sino debe ser un lógica-compuerta-tipo salida con algunas resistencias en serie para proteger contra un evento improbable de un conflicto entre una señal de LIR activo-bajo y un activo-alto la señal de rendimiento de compuerta-lógica. Tal como un conflicto sólo podría ocurrir brevemente al borde cayente de restablecimiento. Desde que LIR es activo por aproximadamente uno fuera de cada tres ciclos durante la ejecución normal (las medias instrucciones toman aproximadamente tres ciclos), IDD podría reducirse por aproximadamente 350 µA (5 V ÷ 4.7 k × 33% deber por ciclo).

Figura 1.19 Conexiones reducidas I DD MODA/LIR

La función de  $V_{STBY}$  es cumplida por un transistor interruptor que conecta  $V_{STBY}$  o  $V_{DD}$  a la RAM y restablece la lógica, mientras dependiendo en los niveles relativos de  $V_{STBY}$  y  $V_{DD}$ . El interruptor conecta  $V_{DD}$  a menos que  $V_{STBY}$

está superior más de que el umbral que V <sub>DD</sub>. Un umbral es aproximadamente una gota del diodo (0.7 V) pero varía de la porción a la porción debido a procesar las variaciones. Durante el funcionamiento normal del MCU, V <sub>DD</sub> es el poder abastecedor de la RAM. En una situación de reserva, V <sub>STBY</sub> debe mantenerse a un nivel válido, y RESTABLEZCA debe activarse (tiró bajo) cuando V <sub>DD</sub> las gotas debajo de los límites legales. RESTABLEZCA que siempre debe sostenerse bajo siempre que V DD sea

Pines EXTAL; XTAL; y E (Cristal Oscilador y Reloj):

El pin del oscilador puede ser usado con un cristal externo o un generador externo CMOS-compatible con un reloj. La frecuencia aplicada a estos pines es cuatro veces mayor que el bus deseado de frecuencia (medida E-Clock). El reloj E es la salida del reloj de bus de frecuencia, cuando esto es usado como una señal de referencia básica. Cuando el reloj E esta en bajo (direcciona una porción del ciclo del bus), un proceso interno esta ocurriendo; cuando E esta alto, esta comenzando el dato a existir. El reloj E esta corriendo libre a un cuarto la frecuencia del cristal es tan largo como el oscilador este activo (modo "stop" para todos los relojes).

El Oscilador en el MC69HC11 consiste de una grande de 2 entradas de compuertas NAND. Una de las entradas para esta compuerta es comandada por una señal interna deshabilitando el oscilador cuando el MCU esta en el modo "stop".

La otra entrada es el pin de entrada EXTAL del MCU. La salida de esta compuerta NAND es el pin de salida XTAL del MCU.

EL pin XTAL es normalmente inconcluso cuando usan una entrada de reloj externa de CMOS compatible al pin EXTAL. Sin embargo, de 10  $k\Omega$  a  $100k\Omega$  de resistencia de carga a tierra puede ser usado para reducir interferencia generada por radio frecuencia (RFI) emisión de ruido. La salida XTAL esta normalmente intencionado para mandar un solo cristal, pero XTAL puede ser usado como una salida de reloj 4x hay que tomar especial cuidado para evitar cargas indeseadas. La salida XTAL puede ser amortiguada con un buffer de alta impedancia tal como el 74HC04. o este puede ser usado para mandar la entrada EXTAL a otro M68HC11 MCU. En todos los casos, el layout del circuito de la tarjeta alrededor de los pines del oscilador es manejada con precaución.

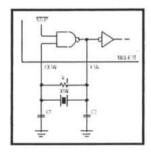

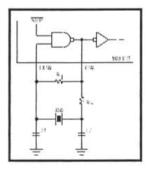

La figura 1.20 y figura 1.21 muestran los componentes internos y externos que forma el cristal oscilador, llamado oscilador Pierce, también conocido como un cristal oscilador paralelo resonante.

Figura 1.20 muestran la conexión para cristales de alta frecuencia (mayores que 1 MHz). La figura 1.21 muestra la conexión para la operación de baja frecuencia (menos que 1 MHz). El resistor, R<sub>f</sub>, provee una corriente directa para la entrada y sólo la NAND opera en esta región lineal. En la conexión de baja frecuencia, Rs y C2 provee un cambio de fase.

R<sub>S</sub> también limita la alimentación dentro del cristal, lo cual es importante para muchos cristales pequeños porque ellos son diseñados para muchos niveles bajos (tipicamente 1-μW máximo). En aplicaciones de alta frecuencia (ver figura 1.20), la impedancia de salida de la compuerta NAND, combinada con la baja impedancia de C1 y C2, provee el mismo efecto con R<sub>S</sub> en diseños de baja frecuencia. Frecuencia alta cristales "a-corte" son diseñados para manejar niveles altos.

Valores exactos para componentes externos son una función de procesamiento ancho de parámetros, capacitores, circuito impreso (PCB) capacitancia e inductancia, conector de capacitancia, operación de voltaje, tecnología de cristal, y frecuencia.

## Valores típicos son:

$R_f$ = 1 M $\Omega$  – 20 M $\Omega$  Valores altos son sensibles a la humedad; valores bajos reducen ganancia y pueden prevenir inicios repentinos.

C<sub>1</sub>= 5 pF - 25 pF Valores usualmente fijos.

C<sub>2</sub>= 5 pF - 25 pF Valores pueden variar para ajustar frecuencia.

Figura 1.20 Conexión del cristal de alta frecuencia.

Figura 1.21 Conexión del cristal de baja frecuencia.

Líneas potencialmente ruidosas deberán ser alejadas tan lejos como sea posible de los componentes del oscilador. Conexiones a tierra deberán ser evitados alrededor de los componentes del oscilador.

#### El Pin de Reinicio "RESET":

Este esta activo en bajo, control de señales bidireccional, es usado como una entrada para inicializar el MC68HC11F1 para un reconocimiento de estado de inicio y como una salida de compuerta abierta para indicar que hay un fallo interno que puede ser detectado en cualquiera de los dos ya sea el reloj del monitor o el circuito guardián de la operación apropiada de la computadora (COP). Esta señal de RESET es significativamente diferente de la señal de RESET usada en antiguos MCU's.

El circuito de reset esta específicamente diseñado para trabajar con bajos niveles de  $V_{DD}$  que otro circuito MCU. De esta forma, puede ser usado para prevenir un funcionamiento indeseado como cuando es aplicado  $V_{DD}$  o decae, lo cual es importante para aplicaciones en lo cual el contenido dentro de RAM debe ser mantenida en la ausencia de  $V_{DD}$ . En esta situación, la memoria RAM y la entrada lógica de reset en el MCU será energizado de la fuente de poder de standby conectado al pin MODB/V  $_{\rm STBY}$  sin embargo  $V_{\rm DD}$  es también bajo para soportar la operación apropiada del MCU. Segundo, RESET deberá ser controlado cuando  $V_{\rm DD}$  esta operando legalmente en los limites, para prevenir una no intencionada corrupción de los datos de EEPROM. Aun si una aplicación no esta usando los 512-byte EEPROM, el registro CONFIG esta fijo en EEPROM y deberá ser protegido de corrupción.

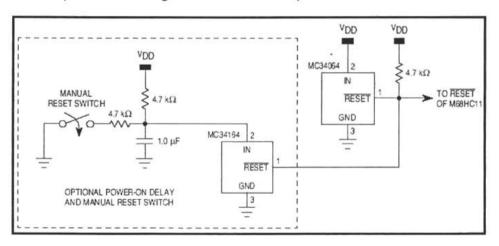

Virtualmente todos los sistemas MC68HC11 deberán incluir automáticamente control de RESET para manejar este bajo siempre y cuando  $V_{DD}$  este legalmente dentro de los limites. Un simple y barato, voltaje bajo inhibe el dispositivo (LVI) tal como el MC34064 o MC34164 pueden ser usados. El MC34064 es valido en paquetes plásticos TO-92 o SOT-8 y provee una salida de compuerta abierta para mandar directamente al pin de RESET del MC68HC11. Este componente es conectado a  $V_{DD}$ ,  $V_{SS}$ , y el pin RESET del MCU. Un paro de la resistencia de RESET a  $V_{DD}$  es el único componente requerido para el circuito de reset en muchas aplicaciones. La figura 1.22 muestra un típico circuito de reset.

Figura 1.22 Circuito de reset

El pin de salida Reloj-E (E)

E es la conexión de salida para el reloj E internamente generado, La señal de E es usada como una referencia de sincronización. La frecuencia de salida del reloj E es un cuarto que de la frecuencia de entrada al pin EXTAL. Cuando la salida del reloj-E es baja, un proceso interno esta tomando lugar. Cuando este es alto, los datos están siendo accesados. Todos los relojes, incluyen el reloj-E, son detenidos cuando el MCU esta en modo STOP. El reloj E puede ser apagado en el modo de chip simple para reducir los efectos de interferencia de radio frecuencia (RFI).

Los Pines de Interrupción (XIRQ e IRQ):

El pin XIRQ provee un recurso para solicitar interrupciones no enmascarables después de la inicialización de reset. Mientras esta reset, el bit X es un juego en el registro de código de condición (CCR), y cualquier interrupción es enmascarada hasta que el software del MCU los habilita. Desde que la entrada XIRQ es nivel sensitivo, esto puede ser conectado a múltiples fuentes de conexión OR con una resistencia de salto. XIRQ es frecuentemente usado como un detector de bajo poder.

La entrada IRQ provee un recurso para solicitar interrupciones asíncronas para el MC68HC11F1. IRQ es programa elegible (registro OPTION), teniendo una elección de cualquier nivel sensitivo o caída de margen sensitivo disparado. Después reset, IRQ es configurado para operación de nivel sensitivo por falta.

Siempre que XIRQ o IRQ son usados con fuentes de interrupción múltiple (IRQ puede ser configurado para operación de nivel sensitivo si hay más que una fuente de interrupción IRQ), cada fuente puede mandar la interrupción de entrada con un tipo de compuerta abierta para evitar conexión entre las salidas. Ahí deberá ser una única resistencia de salto cerca del pin de interruptor de entrada del MCU (normalmente 4.7K).

Ahí debe ser también un mecanismo engrane mecánico a cada fuente de interrupción aunque la fuente mantiene la linea baja de interrupción hasta que el MCU reconoce y acepta la solicitud de interrupción. Si una u otras más fuentes de interrupción están fijos esperando después que el MCU entrega una solicitud, la línea de interrupción se fijará en bajo, de esta manera, el MCU será interrumpido otra vez tan pronto como el bit de mascara de interrupción en el MCU comience a limpiar (normalmente regresa encima de una interrupción).

El pin IRQ es usado durante la fabricación de pruebas como un volumen de  $V_{PP}$  programando fuentes de voltaje, lo cual permite por el paralelo programar de tanto como la mitad de los bytes en la EEPROM en una simple operación de programación. Desde dentro del chip hace una carga que no tiene suficiente capacidad de mando para programar simultáneamente a muchas locaciones EEPROM, la fuente externa de 20 - V es necesaria para suplementar la carga dentro del chip.

El mecanismo de sobre conmutación, el cual decide si la EEPROM esta energizada por la carga interna o la fuente externa de voltaje, es similar para la lógica V<sub>STBY</sub> al pin MODB/V <sub>STBY</sub>. Cuando el voltaje externo es mayor que el voltaje

de la carga interna, la conmutación conecta la fuente externa de alto voltaje a la línea interna V<sub>pp</sub>.

El circuito añadido a este pin no resulta en las funciones normales de IRQ, pero esto hace tener algún efecto dentro del camino el pin responde a niveles ilegales. En adición a XIRQ e IRQ, otros cinco pines en el MC68HC11F1 pueden ser usados también para generar solicitud de interrupciones al MCU. Estos pines están asociados con otros periféricos de chip interno tal como el regulador "timer" o los sistemas de coloquio I/O "handshake". Los pines son PA0/IC3, PA1/IC2, PA2/IC1, PA7/PAI/OC1, Y AS/STRA. El pin de entrada de captura puede ser configurado para detectar un margen de subida o ascendente, margen de bajada o descendente, o cualquier margen. Las entradas PAI y STRA pueden ser configuradas para detectar márgenes ascendentes o descendentes. La entrada STRA sólo es valida se el MCU esta operando en modo de un único chip porque el pin es usado como la salida de dirección "strobe" (AS), cuando el MCU esta en modo expandido. Estos cinco pines tienen ventajas sobre los pines IRQ y XIRQ en que cada uno de estas cinco interrupciones esta independientemente enmascarada con un control local de bit tan bueno como el bit I global en el CCR. Cada una de estas cinco interrupciones también tiene una indicación de estado legible, y una solicitud en espera que puede ser limpiada sin existir entrega.

Los Pines de Referencia A/D y Puerto E (VREFL, VREFH, y PE7- PE0):

Los pines  $V_{REFL}$  y  $V_{REFH}$  proveen las referencias de voltaje para el circuito convertidor A/D. Desde que el convertidor A/D es un circuito convertidor de redistribución toda carga capacitiva, esencialmente no hay corriente cd asociada con estos pines. Muchas dinámicas corrientes pequeñas son causadas por conmutación de redistribución de cargas durante las conversiones. Estos pines son normalmente conectados a  $V_{DD}$  y  $V_{SS}$  a través de una conexión de un filtro paso bajas (ver figura 2-13) para aislar el ruido en la fuente lógica de poder de la relativamente sensitiva medición análoga. Una referencia de fuente de precisión de bajo ruido puede ser usada alternativamente. Ahí deberá ser menor a 2.5 V entre  $V_{REFL}$  y  $V_{REFH}$  para una completa exactitud de A/D. Bajos valores resultaran en más inexactitud, pero el convertidor continuará la operación. El sistema A/D es probado a 4.5 V y 5.5 V a través de los pines de fuente de referencia.

Hay un diodo inherente de V  $_{REFL}$  a  $V_{SS}$ . Si V  $_{REFL}$  va por debajo de  $V_{SS}$  por más que este diodo pequeño diodo, cualquier conversión en progreso puede ser corrompida, pero no un daño físico permanente resultará hasta que una corriente significante este retirada. Los únicos casos documentados de daño han sido causados por una bramante mala aplicación, tal como conectar 12 V directamente al pin  $V_{REFL}$ . Desde ningún dispositivo canal P son asociados con el pin  $V_{REFL}$ , no hay diodo manteniendo  $V_{DD}$ . Las compuertas del conmutador análogo asociada con la referencia A/D y pines de entrada son controlados por señales que conmutan entre  $V_{SS}$  y alrededor de 7V. Esto es mayor que la fuente  $V_{DD}$  y es la salida de la carga (separado de la carga usada para programar en el chip EEPROM).

No hay requerimiento especial para mantener a  $V_{REFH}$  debajo de  $V_{DD}$ . De hecho, el convertidor continuará produciendo buenos resultados arriba de aproximadamente 6 V en V  $_{REFH}$ .

Los pines de entrada del puerto E son usadas para propósitos generales de entradas análogas and/or A/D. Estas entradas son diseñadas así que la entrada del buffers son inhabilitadas todo el tiempo excepto para parte del ciclo durante un lectura actual del puerto E; de este modo, niveles análogos cercanos al punto de conmutación de la entrada digital del buffer no resulta en fuente de alto poder de compuerta de corriente como en una entrada normal de buffer CMOS. Los buffers son habilitados por un dispositivo extra canal N en serie con el dispositivo canal N en la entrada invertida. Durante una lectura digital de puerto E, estos dispositivos canal N extra son encendidos por parte del ciclo de lectura. Porque de este circuito especial, no es necesario para no terminar usado los pines del puerto E.

Las funciones análogas y digitales del puerto E no hace normalmente interferencia con cada otro, así que, cualquier combinación de pines puede ser usada como una entrada digital mientras que los pines restantes del puerto E son usados para entradas análogas. Encendiendo el buffer digital durante una muestra análoga puede causar pequeños disturbios en la línea de entrada, la cual puede causar pequeños errores en el nivel análogo mostrado. Las supuestas perturbaciones causadas por la pequeña compuerta a drenado y compuerta a fuente capacitiva y debe tener para existir una muy cerrada llevando al borde de un periodo muestra para tener cualquier efecto perceptible. Las perturbaciones son tan pequeños (si ellos existen) que ellos probablemente no puedan causar cualquier medición inexacta. Desde que esto es fácil para ordenar el software para evitar esta condición, esto es probablemente fácil para evitar disturbios potenciales.

## El Pin Timer del puerto A:

El puerto A incluye sólo 3 pines de entrada, sólo cuatro pines de salida, y un pin que puede ser configurado para operar como una entrada o como un salida. Los pines de sólo salida (PA0/IC3, PA1/IC2 y PA2/IC1) también sirve como unos pines reguladores de captura de entrada de margen sensitivo. Los cuatro pines de sólo salida (PA3/OC5/OC1, PA4/OC4/OC1, PA5/OC3/OC1 y PA6/OC2/OC1) también sirve como un timer principal de pines de comparador de salida. Siempre que una función de salida compara si esta habilitado, este pin no puede ser usado para una salida de propósitos generales. Estos cuatro pines pueden ser controlados por una salida comparadora1 (OC1) and/or otra salida comparadora. El Pin PA7/PAI/OC1 pueden ser usados como pines de I/O de propósito general, como una entrada de pulso acumulador, o como un pin de salida OC1.

#### Pines del Puerto Serial D

El Puerto D incluye seis fuentes generales, pines I/O bidireccionales que pueden ser configurados individualmente como entradas o como salidas. Cuando la interfase de comunicaciones serial (SCI) receptor esta habilitado, el pin PD0/RxD se convierte en una entrada dedicada a la función RxD. Cuando el transmisor SCI esta habilitado, el pin PD1/TxD se convierte en una salida dedicada para la función TxD. Cuando la interfase del puerto serial (SPI) esta habilitado, los pines PD2/MISO, PD3/MOSI, PD4/SCK y PD5/SS se convierten a dedicados a funciones SPI. Aun mientras el sistema SPI esta habilitado, el pin PD5/SS puede ser usado como una salida de propósito general correspondiendo al local del bit

DDRD5 bit, tal que el sistema SPI esta configurado por modo de operación maestro.

Los seis pines del puerto D puede ser configurado (puerto D conectado-OR modo (DWOM) bit de control en SPI registro de control (SPCR)) para operación conexión OR. Esta opción habilita el canal-P en la salida drivers por lo tanto la salida del puerto D puede activamente conducir en bajo pero no alto, permitiendo dos o más como salidas para ser conectadas sin conexión. Desde el canal P esta físicamente presente (sólo se apaga), hay un diodo inherente del pin de salida a VDD así que el pin no puede ser sacado por el nivel alto que V DD (diferente a una salida Lógica transistor-transistor (TTL) colector abierto). Una resistencia externa de paro es requerido en todas las salidas de los puertos D cuando la opción conexión OR es usada. La conexión fija el programa bootloader configura el puerto D para operación en conexión OR cuando el MCU este reiniciado en modo bootstrap.

Si la aplicación esta usando modo bootstrap cualquiera de los dos apagará la opción conexión OR después de descargado o fuente externa para sobre los resistores de los pines de salida del puerto D.

# 1.6 Instrucciones para las entradas y salidas

La familia 68HC11 está compuesta por microcontroladores (MCU) de 8 bits de gama media-alta (equiparable al conocido 8051 en prestaciones y precio). El 68HC11 se introdujo en el año1985 como actualización de un MCU más antiguo, el 6801, siendo su orientación inicial las aplicaciones de automoción, como encendido electrónico, control electrónico del motor, etc. (compañías como General Motors, Chrysler, Volkswagen o Toyota lo emplean en sus automóviles). No obstante, el HC11 se viene empleando en todo tipo de aplicaciones de consumo, telecomunicaciones e industriales (cámaras fotográficas y video, teléfonos, instrumentación biomédica, etc.), siendo uno de los MCU más populares en todo el mundo.

Se comercializan ejemplares del 68HC11 que operan a 3 y 5V, y a frecuencias de reloj de 2 a 5 MHz. Nuestro kit está diseñado para ejemplares que se alimentan a 5V y operan a 2 MHz (que el HC11 genera a partir de un cristal externo de 8 MHz, que internamente divide por 4). Estas frecuencias relativamente pequeñas no deben llevar a engaño, pues aunque algunos MCU de otros fabricantes operan a frecuencias más altas, los de Motorola realizan un ciclo de bus (acceso a memoria) en un único ciclo de reloj, mientras que otros (como los Intel) precisan tres, cuatro o más, de modo que los MCU de Motorola operando a frecuencias inferiores pueden obtener un rendimiento superior. Por otro lado, debido a que el diseño del HC11 es estático no necesita refrescar sus registros internos, por lo tanto, no presenta un límite inferior en su frecuencia de reloj (de modo que en las aplicaciones de bajo consumo puede reducirse todo lo que sea preciso).

Su bus de direcciones es de 16 líneas, por lo tanto puede direccionar hasta 64 KB (aunque algunos de sus miembros pueden direccionar más de un megabyte), y aunque el bus de datos es de 8, trabaja fácilmente con datos de 16 bits. Todas las

versiones del 68HC11 pueden presentar sus buses al exterior para trabajar con memoria externa.

El 68HC11 posee dos registros acumuladores de 8 bits (Fig. 1), el A y el B; ambos juntos constituyen además un acumulador D de 16 bits (A y B pueden utilizarse libremente como dos registros independientes o como uno único D). También dispone de dos registros índice de 16 bits, el X y el Y, un registro contador de programa PC y un puntero de pila, SP, también de 16 bits. El registro de estado, denominado CCR (condition code register), incluye 8 señalizadores o flags: C (acarreo), V (desbordamiento), Z (resultado cero), N (resultado negativo), H (acarreo a la mitad), I (máscara de las interrupciones IRQ), X (máscara de las interrupciones XRQ) y S (máscara de la instrucción STOP empleada para el estado de bajo consumo).

El 68HC11 cuenta con siete modos de direccionamiento (los mismos que el 6800): directo, extendido, inmediato, indexado, inherente, acumulador y relativo. Su juego de instrucciones posee más de 300 códigos de operación (incluyendo los del 6800 como subconjunto); algunos códigos de operación se componen de un byte y otros de dos (pre-byte y opcode), de modo que una instrucción en total ocupa entre 1 y 4 bytes.

| Vector<br>interrupción      | Dispositivo                                                                      | Máscara en el CCR | Máscara<br>Específica<br>Ninguno |  |

|-----------------------------|----------------------------------------------------------------------------------|-------------------|----------------------------------|--|

| FFC0 a FFD5                 | Direcciones reservadas                                                           | Ninguno           |                                  |  |

| FFD6, FFD7                  | SCI: Registro receptor de datos lleno                                            | ī                 | RIE                              |  |

|                             | SCI: Receptor sobre-escrito                                                      | 1                 | RIE                              |  |

|                             | SCI: Detección de línea inactiva                                                 | 1                 | ILIE                             |  |

|                             | SCI: Registro transmisor de datos vacío                                          | 1                 | TIE                              |  |

|                             | SCI: Transmisión completa                                                        | 1                 | TCIE                             |  |

| FFD8, FFD9                  | SPI: Transmisión serie completa                                                  | 1                 | SPIE                             |  |

| FFDA, FEB                   | Flanco de entrada acumulador de pulsos                                           | 1                 | PAII                             |  |

| FFDC, FFDD                  | Acumulador de pulsos lleno                                                       | Ĭ                 | PAOVI                            |  |

| FFDE, FFDF                  | Temporizador desbordado                                                          | 1                 | TOI                              |  |

| FFE0, FFE1                  | Temporizador OC5                                                                 | 1                 | OC5I                             |  |

| FFE2, FFE3                  | Temporizador OC4                                                                 | 1                 | OC4I                             |  |

| FFE4, FFE5                  | FE4, FFE5 Temporizador OC3 FE6, FFE7 Temporizador OC2 FE8, FFE9 Temporizador OC1 |                   | OC3I                             |  |

| FFE6, FFE7                  |                                                                                  |                   | OC2I                             |  |

| FFE8, FFE9                  |                                                                                  |                   | OC1I                             |  |

| FFEA, FFEB                  |                                                                                  |                   | IC3I                             |  |

| FFEC, FFED Temporizador IC2 |                                                                                  | 1                 | IC2I                             |  |

| FFEE, FFEF                  | Temporizador IC1                                                                 | 1                 | IC1I                             |  |

| FFF0, FFF1                  | Interrupción en tiempo real (RTI)                                                | 1                 | RTII                             |  |

| FFF2, FFF3                  | IRQ (pin externo o E/S paralelo)                                                 | 1                 | Ninguno                          |  |

|                             | IRQ: Puerto E/S paralelo                                                         |                   | STAF                             |  |

| FFF4, FFF5                  | F4, FFF5 Pin XIRQ                                                                |                   | Ninguno                          |  |

| FFF6, FFF7                  | 6, FFF7 SWI                                                                      |                   | Ninguno                          |  |

| FFF8, FFF9                  | 8, FFF9 Opcode ilegal                                                            |                   | Ninguno                          |  |

| FFFA, FFFB                  |                                                                                  |                   | NOCOP                            |  |

| FFFC, FFFD                  | C, FFFD Monitor de reloj                                                         |                   | CME                              |  |

| FFFE, FFFF                  | RESET                                                                            | Ninguno           | Ninguno                          |  |

Tabla 1.4 Tabla de vectores de interrupción del 68HC11.

El sistema de interrupciones del 68HC11 es muy amplio (Tabla 1.4), comprendiendo las clásicas RESET, interrupción enmascarable IRQ, no

enmascarable XIRQ (similar a la NMI del 6800) y software SWI, más una veintena adicionales asociadas a los bloques internos (COP, monitor de reloj, RTI, temporizadores, acumulador de pulsos, SCI y SPI).

Los mC de la familia del 68HC11 pueden trabajar en cuatro modos de operación, dos normales y dos especiales: sencillo (single-chip) y expandido (expanded), especial de test (special test) y especial de arranque (bootstrap). Estos modos se establecen mediante dos patillas, MODA y MODB. Tras la señal de reset la CPU mira el estado de estos pines y establece su modo de operación según los valores presentes en ellos (Tabla 1.5), el cual no es modificable posteriormente por software. En modo simple el HC11 utiliza únicamente sus recursos integrados. El modo expandido se emplea sólo si la memoria interna no es suficiente o se necesitan más puertos; en este caso el HC11 sacrifica dos de sus puertos (el B y el C), cuyas 16 patillas se convierten en los buses multiplexados) del sistema. El modo especial de bootstrap se utilizará para programar desde un PC la EEPROM interna; finalmente, el modo especial de test es empleado por Motorola para la comprobación del chip.

| MODB | MODA | Modo seleccionado                      |

|------|------|----------------------------------------|

| 1    | 0    | Sencillo                               |

| 1    | 1    | Expandido                              |

| 0    | 1    | Especial: test                         |

| 0    | 0    | Especial: arranque externo (bootstrap) |

Tabla 1.5 Modos de operación del MC68HC11.

# 1.7 Instrucciones para la lectura y escritura

La nomericlatura siguiente se usa en las definiciones subsecuentes.

#### operadores:

() = Los contenidos de registro mostrados dentro de los paréntesis

← = Se transfiere a

↑ = Se saca de la pila

↓= Es colocada en la pila

· = And Booleana

+ = El símbolo de suma aritmético excepto dónde es usado como el símbolo de inclusivo-OR en la fórmula de Booleana

+ = OR exclusivo

x = Multiplicación

: = Concatenación