# DIVISION DE ESTUDIOS DE POSGRADO Facultad de Ingeniería

# DISEÑO DE UN SISTEMA DE DESPLIEGUE DE IMAGENES

## JAIME ALARCON CELIS

TESIS

PRESENTADA A LA DIVISION DE ESTUDIOS DE POSGRADO DE LA FACULTAD DE INGENIERIA

DE LA

UNIVERSIDAD NACIONAL AUTONOMA DE MEXICO

COMO REQUISITO PARA OBTENER

EL GRADO DE

MAESTRO EN INGENIERIA

(ELECTRONICA)

CIUDAD UNIVERSITARIA

TESIS CON FALLA DE ORIGEN

UNAM – Dirección General de Bibliotecas Tesis Digitales Restricciones de uso

# DERECHOS RESERVADOS © PROHIBIDA SU REPRODUCCIÓN TOTAL O PARCIAL

Todo el material contenido en esta tesis esta protegido por la Ley Federal del Derecho de Autor (LFDA) de los Estados Unidos Mexicanos (México).

El uso de imágenes, fragmentos de videos, y demás material que sea objeto de protección de los derechos de autor, será exclusivamente para fines educativos e informativos y deberá citar la fuente donde la obtuvo mencionando el autor o autores. Cualquier uso distinto como el lucro, reproducción, edición o modificación, será perseguido y sancionado por el respectivo titular de los Derechos de Autor.

## DISEMO DE UN SISTEMA DE DESPLIEGUE DE IMAGENES.

#### RESUMEN:

En el presente trabajo se describe el diseño de un Sistema de Despliegue de Imágenes construido en base a una microcomputadora.

Se exponen las principales características de los sistemas de graficación y procesamiento de imágenes y se plantean los requisitos que debe satisfacer el Sistema de Despliegue de Imágenes.

Se explica como funciona el sistema en forma general y se describe con detalle cadá uno de los módulos que lo constituyen, dándose a conocer la filosofía con que fue diseñado.

Se describen los diferentes modos de operación del sistema, los cuales son seleccionados de acuerdo al tipo de transformación que se desea aplicar a la imagen desplegada.

|          |      | INDICE                        | PAG. |

|----------|------|-------------------------------|------|

| INTRODUC | CION |                               | 1    |

| Capitulo | 1    | DESCRIPCION GENERAL           | 5    |

| Capitulo | 11   | MEMORIA DE REFRESCAMIENTO     | 16   |

|          | 2.1  | MEMORIA PRINCIPAL             | 17   |

|          | 2.2  | MEMORIA DE BIT DE GRAFICA     | 26   |

| Capitulo | 111  | MEMORIAS AUXILIARES           | 29   |

|          | 3.1  | MEMORIA DE FUNCION            | 30   |

|          | 3.2  | MEMORIA DE SEUDOCOLOR         | 31   |

| Capitulo | IV   | DISPOSITIVOS AUXILIARES       | 38   |

|          | 4.1  | FALSO COLOR                   | 39   |

|          | 4.2  | CLASIFICADOR                  | 43   |

|          | 4.3  | CURSOR                        | 47   |

|          | 4.4  | DIGITALIZADOR                 | 51   |

| Capitulo | V    | INTERFASE Y CONTROL           | 53   |

|          | 5.1  | SELECTOR DE MEMORIA PRINCIPAL | 54   |

|          | 5.2  | SELECTOR DE BIT DE GRAFICA    | 57   |

|          | 5.3  | CONTROL                       | 60   |

|          | 5.4  | SELECTOR VERTICAL             | 67   |

|          | 5.5  | CONVERTIBOR DIGITAL/ANALOGICO | 70   |

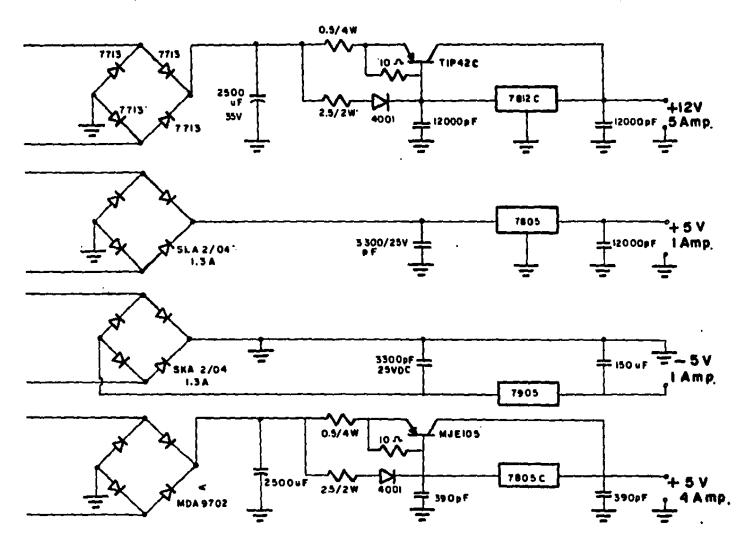

|          | 5.6  | INTERFASE Y FUENTE            | 73   |

|          | 5.7  | PALABRA DE CONTROL            | 79   |

| Capitulo | VI   | CONCLUSIONES                  | 85   |

| BIBLIOGR | AFIA |                               | 92   |

#### INTRODUCCION

En los áltimos años los sistemas de graficación interactivos han tenido un gran desarrollado y una radical evolución. Debido principalmente al avance tecnológico de los circuitos integrados con el cual se ha logrado un mayor progreso

en el desarrollo de "hardware" para los sistemas de graficación y despliegue de imágenes.

Los primeros sistemas de graficación estaban ligados a una "macro-computadora" la cual controlaba y procesaba la información proporcionada por el sistema de graficación. En la última década, la introducción de la minicomputadora libera a dichos sistemas del ambiente en que se encontraban y hace posible la introducción del primer sistema comercial.

Uno de los factores que ha contribuido al desarrollo de los sistemas de graficación es el incremento de las microcomputadoras de bajo costo y con mayor capacidad de procesamiento de información.

Esto se debe a la nueva generación de microprocesadores más poderosos y a una mayor integración del "software" a nivel "firmware". El avance tecnológico alcanzado en los circuitos integrados ha provocado que se abran las puertas del mercado a los sistemas interactivos en función de que esta tecnología es accesible a la gran mayoría de los usuarios, lo que propicia el surgimiento de nuevas áreas de aplicación al igual que nuevos usuarios, y posibilita una mayor interacción entre hombre-máquina y da como resultado un enorme impacto en el desarrollo de nuevos sistemas de graficación y

procesamiento de imágenes interactivos.

La importancia de los sistemas de graficación y los sistemas de procesamiento de imágenes, consiste en la capaci dad que proporcionan para el uso de información gráfica en la comunicación con los sistemas de cómputo. Las imágenes que desean desplegarse pueden ser generadas por programas de computadora usando para su despliegue dispositivos de salida tales como displays tipo "raster-scan", siendo necesario contar con dispositivos de graficación para la entrada, tales como: teclados, "joystics" y tabletas de graficación y en algunos casos, se cuenta también, con dispositivos más sofisticados para la entrada de imágenes como las cámaras de televisión del tipo raster-scan.

Por muchos años los sistemas de graficación y procesamiento de imágenes han sido tratados como temas independientes. La razón de ésto se debe, en gran parte a las diferentes tecnologías que se han usado para los displays desde el comienzo de los sistemas de graficación hace más de 20 años.

Los sistemas de graficación han usado dispositivos de salida como son los displays a través de lineas, pero estos no han sido aceptados para el procesamiento de imágenes debido principalmente a los siguientes factores: intensidades, repetición de vectores, capacidad de color y la memoria de refrescamiento para desplegar tonos continuos o imágenes de color.

Simultáneamente la tecnologia para el procesamiento de

imágenes desarrolló nuevos sistemas, y en lugar de utilizar display a base de lineas, se utilizaron arreglos individuales de "picture element" (pixels). Los displays utilizados para estos arreglos son los monitores de TV standar en combinación con arreglos de memoria en los cuales se encuentra almacenada la intensidad y el color para cada pixel. Sin embargo este tipo de tecnología no cumplió satisfactoriamente los requerimientos de los sistemas de graficación y procesamiento de imágenes debido, principalmente, a la baja resolución de los monitores de TV y al costo relativamente alto de los bancos de memoria.

Hoy en dia el desarrollo de "hardware" para los sistemas de graficación y procesamiento de imágenes está basado en los sistemas de despliegue de alta resolución los cuales ofrecen una mayor cantidad de puntos posibles de direccionar individualmente.

Los displays utilizados en los sistemas de graficación y procesamiento de imágenes tienen dos atributos los cuales son de interes principal: resolución y color.

A pesar de la rápida aceptación de los displays de rastreo en aplicaciones de graficación, estos no son empleados hasta que se empiezan a ofrecer sistemas de despliegue de alta resolución. El color, ha llegado a ser esencial para aplicaciones de diseño de circuitos impresos. Sin embargo las terminales que utilizan refrescamiento por vectores son comúnmente empleadas en aplicaciones en donde se requieren modelos dinámicos, entre éstos se encuentran los diseños mecánicos en que se requiere rotación, traslación y una variedad de operaciones

nes en 3-dimensiones.

Los sistemas de graficación y procesamiento de imágenes cuentan hoy con arquitecturas basadas en microprocesadores, Este tipo de arquitectura facilita— la selección y manipulación de cada uno de los elementos (pixels) que se despliega sobre el monitor. Además, este tipo de dispositivos se encarga de interactuar con el control del sistema para el despliegue de una imagen en todo el rango de sus intensidades cromáticas y establece al mismo—tiempo—el control de cada uno de los pixels. Los diseños que se basan en microprocesadores hacen posible la generación de vectores de graficación con lo cual se puede tener, en un sistema de este tipo, cubiertas las necesidades de los usuarios de los sistemas de graficación y procesamiento de imágenes.

#### CAPITULO I

#### DESCRIPCION GENERAL

El uso de sistemas de cómputo así como de sistemas electrónicos auxiliares para la graficación y el procesamiento de imágenes se ha popularizado, creando una extensa gama de equipos y programas diseñados para este fin. Esto ha permitido que la información obtenida de una imagen digitalizada pueda ser sometida a una gran variadad de análisis con el objeto de obtener un mejor manejo, clasificación y fotointerpretación de imágenes multiespectrales.

Actualmente existen en el mercado sistemas de graficación con arquitecturas y tecnologías muy diversas. Básicamente estos sistemas están constituidos principalmente por un control para el manejo y procesamiento de información, un banco de memoria para almacenar la información digitalizada y un display o CRT (CATODE RAY TUBE) policromático para el despliegue de imágenes.

Una imagen multiespectral digitalizada implica el manejo de grandes volúmenes de información. La cantidad de información depende del número de bits involucrados en la conversión análogo/digital, del número de bandas espectrales digitalizadas y del número e información asociada a cada pixel.

Debido a los grandes volúmenes de información que son obte nidos al digitalizar una imagen, se requiere de un control que sea capaz de almacenar, transferir y procesar dicha información de manera confiable y eficiente. lo cual es posible

al emplear un sistema de cómputo o una unidad central de procesamiento (CPU).

Los datos que se almacenan en el banco de memoria provienen de la conversión análogo/digital de cada una de las densidades cromáticas involucradas en la digitalización, ya sea

que se trate de imágenes monocromáticas (blanco y negro) o

imágenes policromáticas, donde se involucran los tres colores

primarios (ROJO, VERDE, AZUL) y en ocaciones se requiere de

una cuarta banda para los infrarojos.

El display o CRT policromático, es el dispositivo de salida mediante el cual es posible desplegar la información almacenada en memoria; este dispositivo establece un ambiente interactivo entre el sistema de despliegue y el fotointérprete encargado de analizar la información desplegada.

Con el fin de satisfacer las necesidades existentes en el país (localización de cultivos, análisis geotérmico, estudios meteorológicos, etc.) e investigar, en el campo de los sistemas de graficación y procesamiento de imagenes, se propuso el diseño e implementación de un equipo para el procesamiento de imágenes multiespectrales.

Un sistema de análisis multiespectral fundamentalemente es utilizado para el despliegue de imágenes, con el objeto de realizar el estudio de sus densidades cromáticas.

El equipo diseñado satisface algunas de las necesidades existentes en el campo de la percepción remota, en cuanto a poder localizar campos y parcelas sobre el terreno. Desplegando en forma fiel sus colores, tal como fueron tomados por el sensor, lo que permite al fotointérprete interactuar y

participar en el análisis total de una imagen.

El equipo diseñado es altamente interactivo y sirve como medio de comunicación pictórica entre el hombre y la máquina (microcomputadora).

A continuación se listan algunas de las tantas aplicacione nes que tienen estos sistemas:

- -Detección de cultivos por computadora.

- -Mapas de uso de suelo por computadora.

- -Investigación y desarrollo de técnica de percepción remota por computadora.

- -Procesamiento de imágenes por computadora.

- -Tomografia.

- -Modelos digitales de terrenos (Curvas de nivel, carreteras, ríos, cuencas tributarias).

- -Geotermia.

- -Detección de tierras osciosas.

- -Determinación de las parcelas a muestrear para pronóstico de cosechas mediante técnicas de métodos estadisticos de muestreo

- -Fotointerpretación ayudada por computadora.

- -Planeación regional y subregional.

#### PLANTEAMIENTOS PARA EL DISENO

En cualquier proyecto de investigación es necesario realizar un planteamiento general del diseño, con el propósito de delimitar la magnitud del problema a resolver. Dichos planteamientos se realizan, tomando en consideración las opiniones de los posibles usuarios del dispositivo a diseñar, con el objetivo de obtener un sistema que satisfaga sus necesidades.

Los puntos que se deben tomar en cuenta al especificar los planteamientos para el diseño son: El propósito; la fina-lidad y los objetivos a alcanzar en el proyecto.

Para el sistema de despliegue los planteamientos que se establecieron son los siquientes:

#### PROPOSITO:

-Desplegar imágenes en color tomadas desde satélite o avión para ser analizadas por un fotointérprete.

#### FINALIDAD:

- -Dar apoyo al proyecto de percepción remota del IIMAS.

- -Investigar otros campos de la electrónica.

- -Crear un dispositivo, competitivo en el mercado, para muy diversas aplicaciones.

- -Moderna tecnología.

- -Aplicación del avance tecnológico al desarrollo de un nuevo dispositivo.

#### OBJETIVOS.

- -Desplegar una matriz de 256 X 256 pixels en un monitor de color.

- -Cada pixel estará formado por una combinación de los colores fundamentales: ROJO, VERDE, AZUL y se tendrá información adicional en INFRAROJO.

- -Cualquier fotografia podrá ser mapeada a otros valores (intensidad) con cualquier función sin perder la fotografia original.

- -Clasificará pixels dentro de rangos dados.

- -Podrá intercambiarse la información entre los cañones del monitor (falso color).

- -Podrá mapearse cualquier color o el infrarojo a los tres cañones del monitor (seudocolor).

- -Cursor para selección de información.

- -Digitalizador (DMA).

- -Interfase para un sistema de cómputo.

- -Número de bits por color de acuerdo al siguiente planteamiento:

COLOR BANDA

| <b>!</b> |        | • |      | • |     | INTENSIDADES | • |     | 1 |

|----------|--------|---|------|---|-----|--------------|---|-----|---|

| 1        | VERDE! | 7 | BITS | 1 | 128 | INTENSIDADES | 1 | (1) | Į |

| 1        | AZUL ! | 7 | BITS | t | 128 | INTENSIDADES | ł | (2) | 1 |

|          |        | 7 | BITS | 1 | 128 | INTENSIDADES | ļ | (3) |   |

Longitud de la palabra (MEMDRIA DATOS)

| 7 |  | <br>7 | <br>7 | <br>7     |  |  |

|---|--|-------|-------|-----------|--|--|

|   |  |       |       | INFRAROJO |  |  |

|   |  | <br>  | <br>  | <br>      |  |  |

10 20 30

BIT DE GRAFICA (UNO POR BANDA)

-PALABRA DE 32 BITS (DESPLIEGUE).

## ARQUITECTURA DEL SISTEMA.

En el presente trabajo se integran las características de diseño y funcionamiento del sistema de Despliegue de Imagenes, el cual en base a una gran memoria de semiconductores permite el almacenamiento y despliegue de una imagen digita-

40

lizada captada o registrada desde un satélite o un avión en forma remota.

En los procesos de graficación y procesamiento de imágenes se aplican algoritmos especializados para manipular o transformar la información digitalizada. Dichos procedimientos se realizan por métodos programáticos (software) de tal forma que el sistema de despliegue de imágenes puede interconectarse con un sistema de cómputo. El equipo que aquí se describe opera bajo el control de un microprocesador de 8 bits (INTEL 8080 ).

El sistema implementado provee al fotointérprete de las siguientes innovaciones y características:

Clasificación por hardware, tablas de función, cuatro bits de graficación, selección de la longitud de la palabra (8 ó 16 bits) para lectura/escritura de información, cursor para la selección de cualquier punto o área de interés sobre la pantalla, diferentes opciones en el despliegue a traves de las tablas de funciones, seudocolor y bits de gráfica que controlan los cañones del CRT para ser utilizado como una pantalla de graficación.

El sistema cuenta además con un digitalizador de imágenes que hace posible su conexión a una cámara de televisión para la digitalización de fotografías.

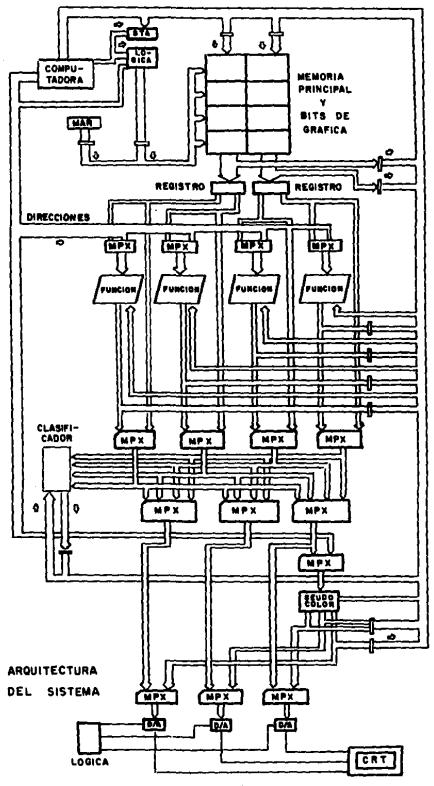

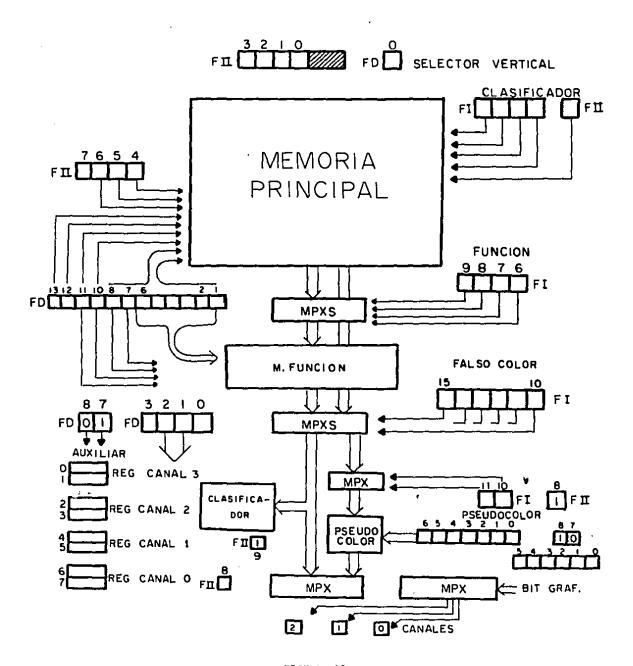

De los planteamientos propuestos para el diseño, se llegó a plantear la arquitectura general del sistema, como se muestra en la siguiente Figura 1.

De esta arquitectura podemos observar que el sistema está

FIGURA 1

constituido por los siguiente módulos:

Memoria de refrescamiento

-Memoria principal

-Memoria de bit de gráfica

Memorias auxiliares

-Memoria de función

-Memoria de seudocolor

-Falso color

-Clasificador

Dispositivos auxiliares

-Digitalizador

-Cursor

-Convertidores digital/analógico

y sincronia

Interfase y control

-Lógica de control

A continuación se da una descripción global de cada uno de estos módulos y posteriormente, se desglozará y explicará el funcionamiento de los mismos.

## MEMORIA PRINCIPAL

Tiene una capacidad de 64K palabras de 28 bits; es una memoria de acceso aleatorio (RAM) microintégrada en tecnología MOS estática, con las siguientes especificaciones:

Tiempo de acceso : < 250 n seg.

Señales de control : Lectura, escritura, chip select

Esta memoria guarda imágenes digitalizadas, y es leida por un circuito para ser desplegada en un monitor a colores.

La información que se almacena en esta memoria será:

4 bandas de 7 bits c/u referentes a las bandas de

intensidades.

Además, la memoria es accesada por un sistema de cómputo (micro-computadora), como su memoria principal por medio de una "ventana".

El circuito de despliegue accesa palabras de 32 bits, mientras que la microcomputadora puede efectuar accesos de 8 ó 16 bits.

#### BITS DE GRAFICA

Esta memoría tiene una organización similar a la memoría princicipal y la información almacenada se encuentra distribuida en:

4 bandas de 1 bit c/u referente a las bandas de gráfica.

Tres de los cuatro bits de gráfica llegan a los cañones del monitor, si alguno de éstos se encuentra encendido, inhibe el paso de la información proveniente de las bandas hacia los cañones, y satura el cañón cuyo bit de gráfica está encendido. Si más de un bit de gráfica está encendido, se saturarán todos aquellos cañones a los cuales llega dicha información.

#### MEMORIA DE FUNCION

En este bloque se cuenta con cuatro arreglos de memoria RA H TBJ con capacidad de 128 palabras de 7 bits c/u, este módulo permite mapear o transformar cada una de las bandas en diferentes intensidades, por medio de una función almacenada en forma de tabla sobre el banco de memoria por el sistema de cómputo, las características de la memoria son:

Capacidad del banco de memoria 128  $\times$  28 bits Capacidad de la pastilla 32  $\times$  2 bits Memoria RAM tecnología TBJ

Tiempo de acceso 50 nseg. max.

Tiempo del ciclo de escritura 45 nseg. max.

## MEMORIA SEUDOCOLOR

El seudocolor es un modo de operación del sistema a elección del programador, para efectuar un mapeo de alguna de las 4 bandas, sobre los 3 cañones del monitor de color. El seudocolor está implementado por la lectura de una memoria en donde se encuentra la dirección asignada el mapeo corres pondiente. Esta memoria se accesa desde la microcomputadora para efectuar la programación de los valores asignados. La organización y características de esta memoria son idénticas a las del módulo de función.

#### FALSO COLOR.

Por medio de este módulo el fotointérprete tiene la opción de multiplexar las bandas del sistema, sobre cualquiera de los tres cañones del monitor, el usuario tiene la capacidad de elegir las combinaciones de los tres colores básicos (ROJO, VERDE o AZUL).

## CLASIFICADOR.

Los pixels son clasificados en tiempo real. Para esto se utilizan 8 registros de 7 bits c/u, los cuales contienen los límites de un cubo (en 4 dimensiones), que definen el área de clasificación.

Estos registros son accesibles al sistema de cómputo. El valor de los registros es comparado con cada una de las ban das de intensidad correspondiente a los pixels, y el resulta-

do de la clasificación se guardara en memoria en alguno de los bits de gráfica.

#### SUBSISTEMAS.

En este bloque se localiza la lógica de control la cual re aliza las siguientes actividades.

-Interfase del sistema de cómputo.

- -Generación de las señales de control para escritura y lectura a memoria.

- -Generación de señales para despliegue.

- -Manejo de la palabra de control.

- -Control de registros especiales.

#### SELECTOR VERTICAL

Modos de acceso a memoria desde el sistema de cómputo.

- -1 Bit (Bit de gráfica).

- -2 Bits (Bit de gráfica).

- -7 Bits (por banda).

- -8 Bits (banda y bit de gráfica).

- -14 Bits (2 bandas).

- -16 Bits (2 bandas y 2 bits de gráfica).

Modos de acceso para el despliegue 32 Bits (4 bandas y 4 bits de gráfica).

## PALABRA DE CONTROL.

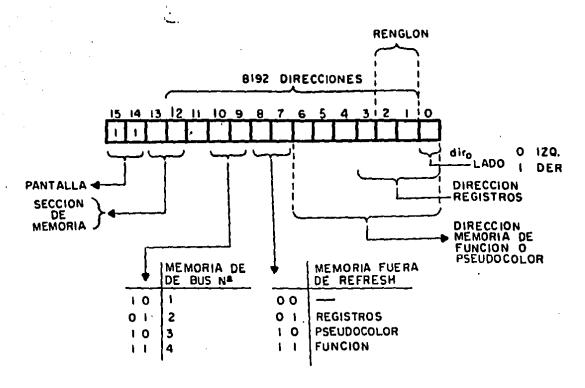

El direccionamiento del sistema se basa en el manejo de una ventana de 16 K por medio de la palabra de control.

La cual indica al sistema de despliegue las actividades que debe realizar. Así como también, coordina las funciones del sistema de cómputo.

#### CAPITULO II

#### MEMORIA DE REFRESCAMIENTO

Esta etapa es la parte central del sistema de despliegue, en ella se almacena la información digitalizada de una imagen multiespectral.

Se le da el nombre de memoria de refrescamiento debido a la similitud que existe con las memorias dinâmicas, en las cuales ocurren ciclos de refrescamiento cada vez que la información es accesada.

Esto también ocurre en los bancos de memoria instrumentados, debido a que la información que se encuentra grabada se accesa continuamente para su despliegue sobre el CRT.

El término de memoria de refrescamiento únicamente se refiere a una convención utilizada en el sistema de despliegue de imágenes y no al tipo de tecnología empleado para la instrumentación de dicho banco.

La Memoria de Refrescamiento está integrada por:

Memoria Principal Nemoria de Bit de Gráfica

## 2.1 \*MEMORIA PRINCIPAL\*

En este bloque se cuenta con un banco de memoria RAM estática de alta velociad de acceso, en él se almacena la imagen digitalizada para su despliegue sobre un monitor de color con un formato de 256 X 256 picture element (pixel).

Las dimensiones del banco de memoria son determinadas por el formato del monitor de color, es decir, a cada uno de los puntos a desplegar en la pantalla, le corresponde una celda de memoria.

La memoria está, constituida por un arreglo de 64K X 28 bits, cuya información corresponde a la imagen en cuatro ban das (verde, rojo, azul e infrarojo) de siete bits cada una, para obtener 128 niveles cromaticos en la conversión digital analógica, como se presenta en la siguiente tabla:

Formato del monitor 256 X 256 = 64K pixels

Formato del banco de 64K X 28 bits

memoria principal

Formato del banco de 64K X 7 bits

memoria principal por

banda.

Niveles cromáticos por 2 \*\* 7 = 128

banda

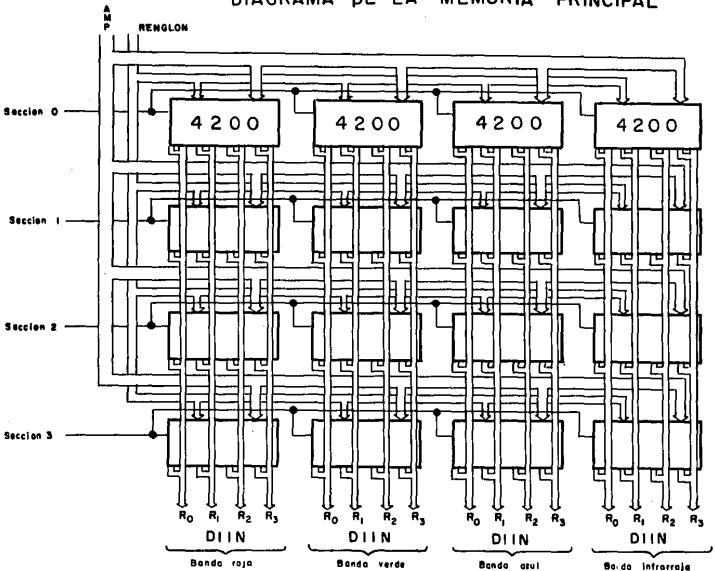

La organización del banco de memoria principal, se realizó en cuatro módulos, correspondiendo uno a cada banda de color. A su vez cada banda se subdividio en 4 secciones y cada sección en cuatro renglones. Como resultado de dicha organiza-

ción se tiene que el manejo de la memoria es en "tubería" o "pipe line".

Debido a las dimensiones de la memoria y a la organización de esta fué necesario instrumentar bancos de 16K X 7 bits de memoria constituyendo una sección con sus cuatro renglones, de tal forma que cuatro tarjetas constituyen una banda teniendo 16 tarjetas para todo el sistema.

Cada una de estas tarjetas es un arreglo de memoria con capacidad de 16K X 7 bits donde se almacena la información correspondiente a una cuarta parte de una banda de color, es tá formada por 28 pastillas de memoria RAM tipo MOS estática con capacidad de 4K X 1 bit cada pastilla, acomodados en cuatro renglones de 7 pastillas cada uno.

#### FUNCIONAMIENTO.

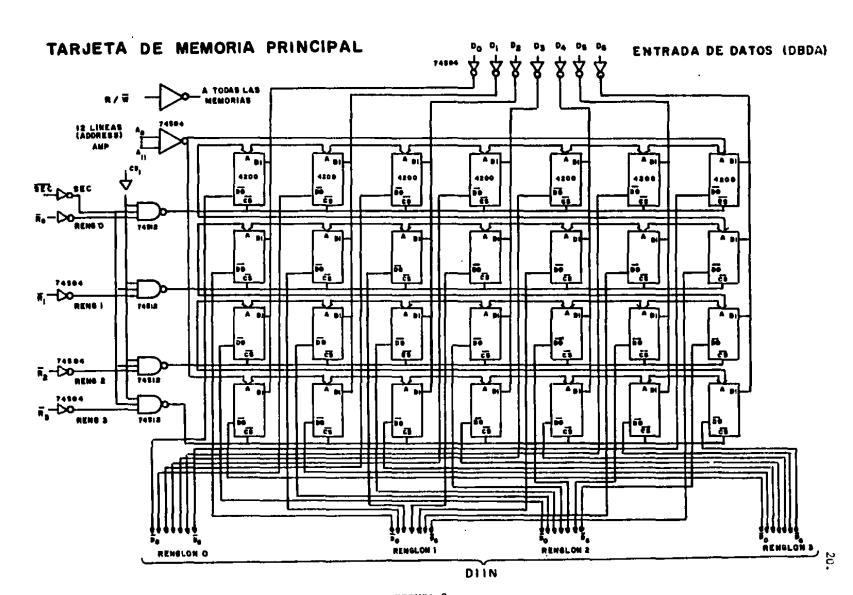

La tarjeta de memoria principal es direccionada con parte del bus de direcciones (AMP), las señales de dirección que se utilizan son 12 (AMPO-AMP11), estas direcciones se presentan simultáneamente en todas las memorias.

La lógica de selección de la memoria es implementada con compuertas nand de 3 entradas cuyas señales de entrada son: CHIP SELECT (CS), SECCION (CSEC) y Renglón (CRO-CR3).

Las señales de CHIP SELECT y SECCION seleccionan una de las 16 tarjetas de la memoria principal del sistema .Las señales de RENGLON seleccionan uno de los cuatro renglones con que cuenta cada tarjeta, indicando la localidad direccionada.

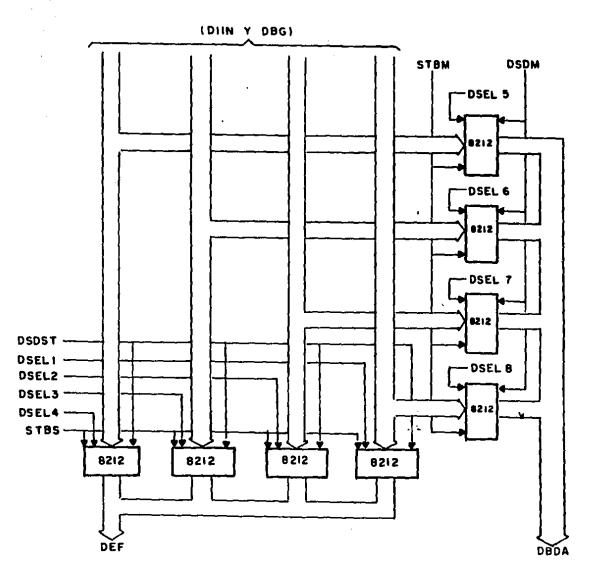

Debido a la arquitectura de la memoria se implemento un

bus de datos de entrada (DBDA) que se conecta simultáneamente a los cuatro renglones de memoria, como se muestra en la figura 2. Cada tarjeta cuenta con cuatro buses de datos de salida (DIIN) de siete bits cada uno que corresponden a los datos de cada renglón.

La arquitectura de la memoria principal se muestra en la figura 3. Como puede apreciarse, cada banda de color está formada por cuatro módulos de memoria conectados en paralelo a través del bus de datos DIIN.

Con el objeto de poder soportar la carga que se presenta a las señales de direcciones, datos, sección, chip select, rengión y lectura/escritura cada una de las tarjetas cuenta con 'drivers' a la entrada de éstas, por lo que dichas señales tendrán únicamente, una carga de cuatro compuertas para todo el sistema.

La información puede ser accesada por el sistema de computo para realizar una lectura o escritura y de acuerdo a la palabra de control estos accesos pueden ser los siguientes:

- -Una banda con su respectivo bit de gráfica.

- -Cualesquiera de los bit de gráfica.

- -Una banda sin bit de gráfica.

- -Dos bandas con/sin bit de gráfica.

Los accesos para el despliegue (solamente lectura) seran de cuatro palabras de 32 bits cada una, las que se almacena-rán en registros temporales que posteriormente se distribuiran en el tiempo para su despliegue sobre el CRT.

La razón por la cual se leerán cuatro palabras es para obtener los tiempos necesarios que requiere el sistema de computo para realizar un acceso a la memoria. Esto se puede ex-

FIGURA 2

# DIAGRAMA DE LA MEMORIA PRINCIPAL

plicar si sabemos que la imagen esta constituida por 256 x 256 pixels desplegándose 30 cuadros/seg., y que cada cuadro consta de dos campos entrelazados siendo uno la repetición del otro teniendose 512 lineas.

El tiempo en el cual se barre una de las 512 lineas de un cuadro est

El tiempo de acceso de la memoria es menor a 250 n seg. y su tiempo de recuperación es menor a 125 n seg. por lo que se requiere un ciclo de 350 n seg. para un acceso.

Se desea tener por cada acceso de despliegue un acceso del sistema de computo (micro) por lo cual para poder cumplir co-rrectamente con los tiempos de despliegue se leerán cuatro pixels en cada acceso, obteniêndose en cada renglón:

Es decir, se tendrá un total de 128 accesos en 65 u seg., teniéndose 500 n seg. por acceso lo que determina una frecuencia de 2 MHz.

Las características técnicas así como los diagramas de tiempos de la memoria empleada para este arreglo son: Descripción General:

La memoria RAM de tecnologia Mos canal N SEMI 4200 tiene tiene una organización de 4096 palabras de 1 bit. Esta usa una celda de memoria completamente estática lo que elimina la necesidad de un circuito de refrescamiento.

Todas las entradas pueden ser manejadas por un circuito TTL y las salidas de tercer-estado pueden directamente manejar cualquier tipo de carga TTL.

#### CARACTERISTICAS:

- Completamente estática.

- Tiempo de acceso 150 nseg. max.

- Tiempo de ciclo 300 aseg. max.

- Potencia tipica en operación 450 mw.

- Potencia tipica en "stand by" 35mw.

- Salidas de tercer estado compatibles con TTL.

- Completamente decodificada.

- Chip select activo bajo.

Las celdas de memoria están organizadas en un arreglo de 64 renglones por 64 columnas (4096 palabras x 1 bit). Cada celda de memoria es direccionada simultaneamente decodificando las direcciones (A0-A5) para renglones y las direcciones (A6-A11) para las columnas.

El dato se escribe o se lee por separado en las entrada (DI) y la salida (DO). La operación de la memoria es controlada por las señales Chip Select (CS) y Read/Write (R/W).

Cuando el CS es alto, todas las señales se encuentran fuera de operación en un estado de alta impedancia, y la potencia es aplicada solamente al elemento de memoria. Cuando el CS es bajo, la memoria es habilitada para lectura o escritura.

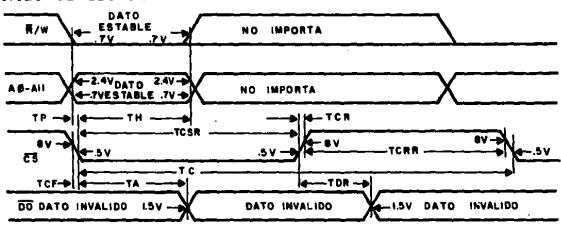

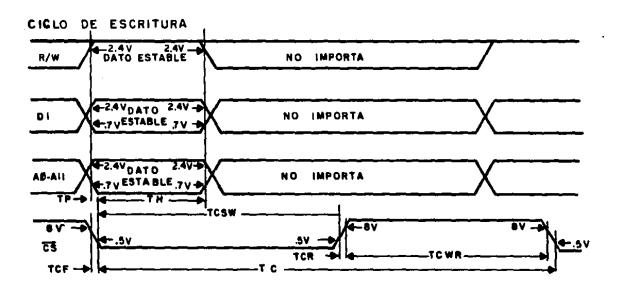

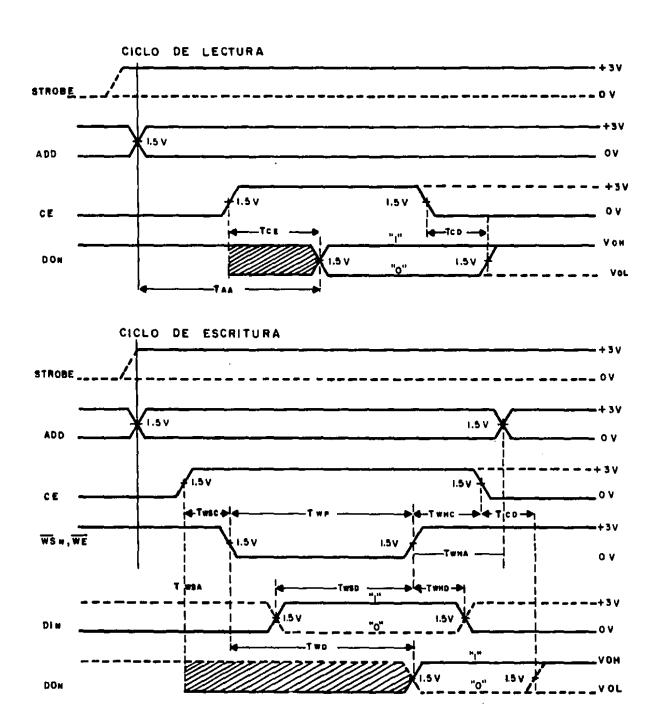

## DIAGRAMA DE TIEMPO CICLO DE LECTURA

El ciclo de lectura comienza con el frente de onda nega tivo de la señal CS. El dato, las señales de R/W y direcciones deben estar estables en el tiempo Th. Las señales de direcciones y R/W son "latcheadas" y no se requiere que esten estables por más tiempo. El dato de salida estara presente en

(DO) durante el tiempo Ta y permanecera hasta el tiempo Tdr despues de que la señal de CS regresa a un nivel alto. Despues del tiempo Tc otro ciclo de lectura o escritura puede iniciarse.

## DIAGRAMA DE TIEMPOS CICLO DE ESCRITURA

El ciclo de escritura comienza también con el frente de onda negativo de la señal CS. Las señales de R/W, direcciones y DI deben estar estables en el tiempo Th.

Estas entradas son "latcheadas" y el dato DI será almacenado en el tiempo Tosw. Otro ciclo de lectura puede ser

iniciado despues del tiempo To.

## CICLO DE LECTURA

## 2.2 \*MEMORIA DE BIT DE GRAFICA\*

En los sistemas de despliegue de imágenes es importante contar con unidades que nos permitan almacenar información adicional a cada uno de los pixels que se están desplegando. Esta información puede ser parte de un texto, vectores de información o resultados de una clasificación de acuerdo a las características que se deseen seleccionar de la imagen desplegada.

Para cubrir estas necesidades y dar al sistema una mayor flexibilidad en el procesamiento de imágenes se diseño una tarjeta de Memoria de Bit de Gráfica, con una capacidad de 16K x 4 bits con lo cual se cubre toda la información de una banda, quedando constituído el sistema con 4 bancos idéntimos, uno para cada banda de color.

## FUNCIONAMIENTO.

Existen dos tipos de funcionamiento de la Memoria de Bit de Gráfica, que son los siguientes:

10. MODO NORMAL. Por las características de implementación de la Memoria de Bit de Gráfica se puede observar que es un arreglo similar al de la Memoria Principal.

En este modo de operación la Memoria de Bit de Gráfica trabaja en paralelo a la memoria principal por lo tanto, el bus de direcciones es el mismo (AMP); el bus de datos en este caso es de ocho bits, tomando en cuenta que el bit más significativo es el de la Memoria de Bit de Gráfica.

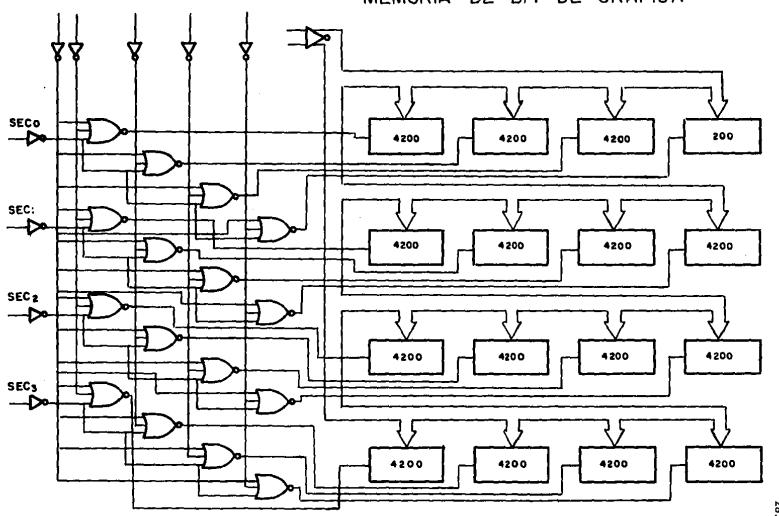

La señal de selección se genera por medio de una lógica combinacional cuyas señales de entrada son: Sección, Renglón y Chip Select (CS), como resultado de esta decodificación se obtiene la misma señal de CHip Select (CS) utilizada por la memoria principal, en la Figura 4 se muestra la arquitectura de la Memoria de Bit de Gráfica.

and the second of the second o

20. MODO DE CLASIFICACION .- Este modo de operación es seleccionado desde el módulo de control, y tiene por objeto habilitar a la Memoria de Bit de Gráfica, para almacenar infor

mación adicional de cada uno de los pixels.

El dato almacenado en esta memoria es el resultado de un proceso de clasificación. La característica más importante en este modo de operación es que el direccionamiento a esta memoria va defasado, con respecto al de la memoria principal en cuatro direcciones, esto es con el objeto de que se realice un ciclo de lectura/escritura; es decir se lee el dato de la memoria principal, y se compara en el modulo del clasificador para obtener la información adicional a cada uno de los pixels, dicha información se escribe en la Memoria de Bit de Gráfica, en la misma localidad de la cual fue obtenido.

Dicho direccionamiento se logra porque en este modo de operación el bus de direcciones de memoria principal y Memoria de Bit de Gráfica son proporcionados por los módulos de selección de memoria principal y Memoria de Bit de Gráfica, respectivamente.

# MEMORIA DE BIT DE GRAFICA

#### CAPITULO III

## "MEMORIAS AUXILIARES"

La finalidad de estos bancos de memoria es la de proporcionar al fotointérprete de las herramientas necesarias para manipular la información que se encuentra almacenada en la memoria principal.

Considerando las necesidades que exige la fotointerpretación de imágenes policromáticas y monocromáticas, el sistema de despliegue cuenta con un banco de memoria auxiliar, mediante el cual es posible realizar transformaciones o mapeos de una imagen.

Estas transformaciones son posibles de efectuar debido a que se dispone de la lógica de control, necesaria para determinar la trayectoria de la información que maneja el sistema de despliegue.

El fotointérprete puede seleccionar a través del panel de control el paso por las memorias de función o seudocolor. A dichas memorias se les denomina memorias auxiliares, porque se presentan como una extensión de la memoria principal.

Las memorias de función y seudocolor tienen como objeto almacenar en forma de tabla la función o las tablas de seudo-color que se desea aplicar a la imagen original.

#### 3.1- MEMORIA DE FUNCION

En muchas ocasiones la información digitalizada de una imagen requiere de ser transformada o "mapeada" bajo una cierta función, esta transformación puede realizarse por software o por hardware.

Si la información digitalizada es transformada por software, implicará dos accesos a memoria (uno de lectura y otro de

escritura) por cada uno de los pixels, así como también

requerirá de tiempo de procesamiento para aplicar la función

a la información digitalizada.

En algunas ocasiones este método de transformación puede resultar inadecuado, ya que la información original se "pierde" y el fotointérprete no puede desplegar simultánea-mente la información original y la información transformada.

El método de transformación por hardware nos permite "desplegar" tanto la información original como la información transformada. Este método se realiza por medio del banco de memoria de función que almacena la función que se desea aplicar a la información original.

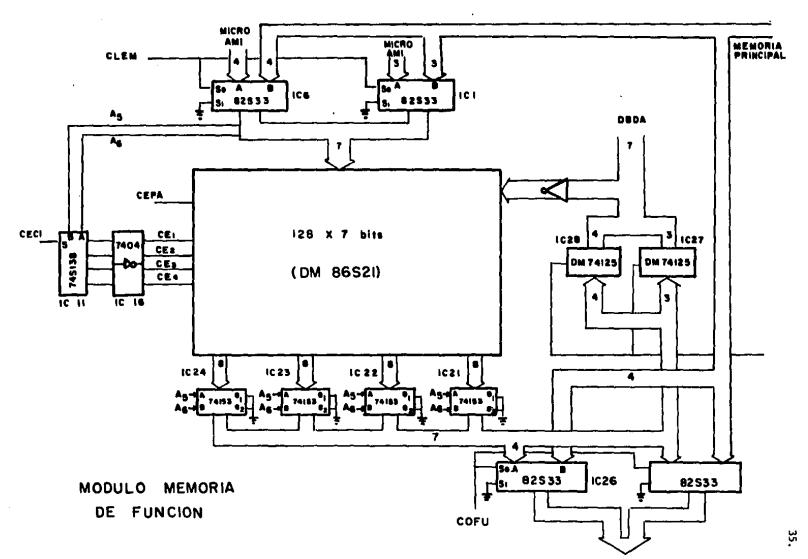

El módulo de memoria de función tiene una capacidad de 128 x 28 bits de memoria RAM TBJ. La implementación de la memoria de función se realizo en cuatro tarjetas correspondiendo una tarjeta por banda. La organización de cada una de estas tarjetas es de 128 x 7 bits y al igual que los demás módulos de memoria cuenta con crivers en los buses de direcciones de datos y de control.

#### 3.2- MEMORIA DE SEUDOCOLOR

Otra de las necesidades de la fotointerpretación es la que existe cuando se manejan imágenes monocromáticas, pues por las tonalidades que se emplean (grises), en ocasiones, se pierden detalles para el ojo humano.

Por estas necesidades surgió la idea de poder "rutear" la información digitalizada de una imagen monocromática para obtener un despliegue policromático.

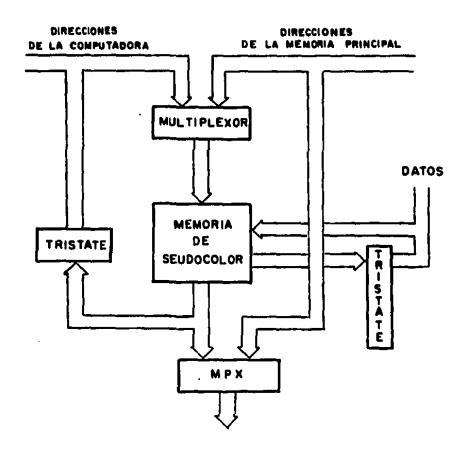

Esto se logra a través de una unidad llamada memoria de seudocolor que se encarga de transformar o "mapear" una benda a los tres colores del sistema de despliegue. La capacidad de esta memoria es de 120 x 21 bits y se encuentra implementad da en tres tarjetas, correspondiendo una a cada color y su organización es idéntica a la memoria de función. En la Figura 5 se muestra un diagrama a bloques de la trayectoria de la información al pasar por la memoria de seudocolor.

FUNCIONAMIENTO DE LA MEMORIA DE FUNCION Y SEUDOCOLOR.

Existen dos formas de operación para estas memorias las cuales son:

- a) Direccionadas por el sistema de computo; para almacenar en forma de tablas la función discretizada o las tablas de seudocolor.

- b) En operación de función o seudocolor: esto se hace a través de la palabra de control por medios programáticos, para seleccionar la operación del modulo de función o el modulo de seudocolor.

MEMORIA DE SEUDOCOLOR

FIGURA 5

En cualquiera de estos dos modos de operación el direc-cionamiento está dado por los datos provenientes de la memoria principal.

La información a la cual se le aplica una función o un "mapeo", es la proveniente de la memoria principal y se en cuentra en el "BUS" de DATOS DE ENTRADA (DDIN).

Este Bus de Datos se localiza a la entrada de dos multiplexores, uno de ellos llamado multiplexor de funciónes el cual selecciona entre la información transformada o mapeada y la información original (DDIN).

El otro multiplexor llamado de direcciones, elige entre el Bus de Datos (DDIN) cuando se aplica la función o el seudo-color y la dirección del sistema de computo (AMI).

Los bancos de memoria de Función y Seudocolor se presentan como una extensión de la memoria principal y si el sistema de computo desea accesar a estas memorias, el modulo de control genera la petición de acceso a la memoria de función o seudocolor por medio de la señal de lectura/escritura a memoria (CLEM).

Si el sistema de cómputo realiza un proceso de escritura para almacenar la función o las tablas de seudocolor el multiplexor de direcciones seleccionará el bus de direcciones del sistema de computo (AMI).

La función que se desea aplicar o las tablas de seudocolor estarán presentes en el bus de datos (DRDA) por medio de la señal de control de habilitación para acceso (CEPA). Si el sistema de computo desea leer la información almacenada en dichas memorias el funcionamiento será similar al an

terior proceso. El módulo de control identifica que es un acceso de lectura y habilita además la señal de control de tercer estado (COTE), que permite que los "drivers" de salida se

activen colocando sobre el bus de datos (DBDA) la información

de las memorias apuntadas por la dirección AMI.

Si se desea aplicar la función sobre la información digitalizada, el procedimiento será como un ciclo de lectura, pero las direcciones a la memoria de función serán los datos de la memoria principal (DDIN) y la señal de control de función (COFU) seleccionara el bus de datos de salida de la memoria de función o seudocolor para su despliegue, en este caso la senal de COTE no se activa. la figura ó muestra el diagrama a bloques de estas memorias.

La información técnica y diagramas de tiempos del circuito integrado de memoria RAM utilizado para implementar los bancos de memoria de Función y Seudocolor es la siquiente:

# DESCRIPCION:

La memoria RAM de tecnología TBJ 82521 tiene una capacicidad de 64 bit organizada en una matriz de (32×32).

Las palabras son seleccionadas por medio de un decodificador de 5 entradas cuando la señal de Chip Enable (CE) se encuentra en un nivel lógico alto. Las señales WSO y WSI son las entradas de selección de escritura para el bit O y el bit 1 de la palabra seleccionada. La señal WE es la linea de control de escritura. Cuando WSn y WE se encuentran en un nivel bajo el dato que se localiza en DIO y DI1 es escrito en

FIGURA 6

la localidad direccionada. La función de lectura es habilitada cuando cualquiera de las señales WSn o WE se encuentra en un nivel alto.

Un latch interno proporciona la capacidad de escribir mientras se lee. Cuando la linea de control del latch (strobe) se encuentra en un nivel alto el dato se lee. El dato a la salida será el de la localidad direccionada. Cuando la señal de control cambia de un nivel alto a bajo el dato es "latcheado" y así permanecen aunque cambien las lineas de direcciones. En la transición de la señal de strobe de bajo a alto el dato cambia y las salidas asumen el contenido de la localidad direccionada.

# CARACTERISTICAS.

- Tiempo de acceso 50 nseg. max.

- Tiempo de ciclo de escritura 45 nseg. max.

- Disipación de potencia 7.5 mw/bit typ.

- Capacidad de la salida 32 ma.

- lineas de control por bit.

- Función de escribe mientras lee.

- Salidas Open-Colector.

- Compatible con TTL.

# CAPITULO IV

# DISPOSITIVOS AUXILIARES

La fotointerpretación implica procedimientos sofisticados para la obtención de resultados. Para realizar estos procedimientos es necesario contar con la herramienta adecuada para efectuar una transformación o un procesamiento de información. Dicha herramienta pueden ser programas para computadora o dispositivos auxiliares dedicados a desarrollar una actividad específica, como clasificar, digitalizar, producir falso color ó emplear curso-res.

El sistema de despliegue cuenta con dispositivos auxiliares, con el propósito de facilitar el manejo de la información tanto para el despliegue como para la adquisición de

datos de un pixel o una imagen, logrando con esto un mayor

poderio del sistema para el procesamiento de imagenes.

Estos dispositivos permiten que el sistema ofrezca diferentes características de funcionamiento como son:

- -El poder direccionar la salida a cualquiera de los 3 cañones de CRT para producir el Falso Color.

- -Clasificación de pixels por hardware, pudiendo ser almacenado el resultado en un plano adicional.

- -Cursor para la selección de un pixel o una área de interés.

- -Digitalizador para la adquisición de información de fotografías aéreas o mapas.

# 4.1- "FALSO COLOR"

Debido a las intensidades así como a los contrastes en imagenes de color en ocasiones, el usuario puede llegar a tener problemas para identificar zonas de interés. Lo anterior puede corregirse en gran, parte si se cuenta con un dispositivo que, nos permita seleccionar las combinaciones cromáticas de una imagen, proporcionando un "Falso color" a la imagen original.

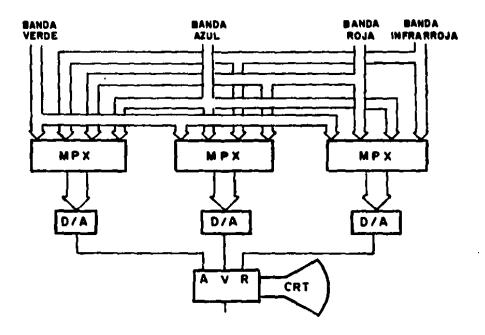

La finalidad del módulo de falso color es el de poder direccionar las bandas a cualquiera de los cañónes del CRT. Un diagrama a bloques del módulo de Falso Color se muestra en la figura 7.

El sistema de cómputo, a través de la palabra de control, puede seleccionar la trayectoria de la información de cada una de las bandas, de tal forma, que la banda roja pueda desplegarse hacia cualquier cañón del CRT, al igual que las bandas verde, azul e infraroja.

#### **FUNCIONAMIENTO:**

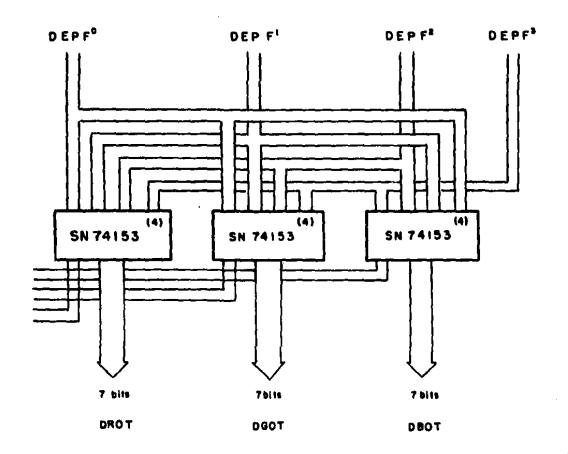

Básicamente la tarjeta de falso color, es un multiplexor 84 a 21 líneas para las tres bandas, este multiplexor esta implementado con 12 circuitos integrados. Como se muestra en la figura 8.

A esta tarjeta arriban 4 buses de 7 bits cada uno (DEFO a DEF3) provenientes del módulo de Memoria Principal o del Módulo de Memoria de Función. Estos buses contienen la información digitalizada de una imagen, con sus colores originales, correspondiendo cada uno a las bandas ROJA, VERDE, AZUL e INFRAROJA respectivamente.

FALSO COLOR

FIGURA 7

FALSO COLOR FIGURA 8

La unidad de control, por medio de seis lineas de selección, (CSAR, CSBR, CSAG, CSBG, CSAB, CSBB) determina el "flujo" de la información proveniente de cada una de las bandas para su despliegue sobre cualquiera de los tres cañones del monitor (DROT, DGOT, DBOT).

El panel de control cuenta con 2 interruptores, por medio de los cuales el usuario proporciona al módulo de control, las señales necesarias para que éste realice la decodificación que habrá de determinar sobre que cañón del CRT se desplegará la información.

La siguiente tabla indica los modos de operación del módulo de falso color.

| 1 | NTER | RUPTO | RES DE | CONTROL  |      |   | SAL  | _[] | DAS  |         |

|---|------|-------|--------|----------|------|---|------|-----|------|---------|

|   |      |       |        |          |      |   |      |     |      |         |

| 1 | CSA  | 1     | CSB    | 1        | OUTR | ł | OUTG | 1   | OUTB | 1       |

|   |      |       |        |          |      |   |      |     |      |         |

| 1 | 0    | 1     | 0      | 1        | R    | 1 | G    | 1   | В    | 10.N.*  |

| • | 0    | 1     | 1      | Ì        | G    | 1 | Ŀ    | ł   | R    | IF.C.** |

| 1 | 1    | 1     | 0      | 1        | В    | ł | R    | 1   | G    | IF.C.** |

| 1 | 1    | 1     | 1      | <b>{</b> | I    | 1 | I    | 1   | 1    | IF.C.** |

|   |      |       |        |          |      |   |      |     |      |         |

\*Operación Normal \*\*Falso Color

Como puede apreciarse en la arquitectura general del sistema, este módulo siempre se encuentra habilitado, trabajando en el MODO NORMAL (CSA = CSB = 0) y únicamente ocurrirà un cambio de color si existe algún cambio de condición en las señales de control. Es importante mencionar que este módulo es completamente transparente al usuario y al sistema ya que únicamente se encarga de intercambiar la información digitalizada para las etapas de video.

# 4.2- CLASIFICADOR

Una de las actividades principales que se realiza en la interpretación y reconocimiento de información contenida en una imagen digitalizada, es el de clasificación.

Esta clasificación se realiza mediante procesos de descriminación de información de acuerdo a sus intesidades cromáticas, si se encuentran o no en un rango de tonalidades previamente determinado.

Como se observa del planteamiento anterior el proceso de clasificación se puede realizar con ayuda de métodos prográmaticos (software). Este método es el tradicional y para su implementación se requiere un acceso a memoria para leer la información digitalizada, procesar dicha información para determinar si se encuentra en el rango de tonalidades deseado y por último accesar a la memoria para grabar el resultado de la clasificación, lo anterior redunda en el factor tiempo y para algunas aplicaciones este método de clasificación puede resultar lento, sobre todo, si se quiere realizar un proceso iterativo. Cabe mencionar que con este método la capacidad de la memoria del sistema de cómputo se reduce ya que el resultado de la clasificación queda almacenado en ésta.

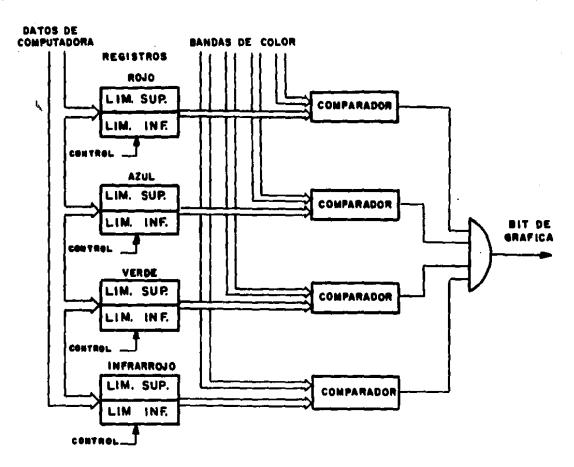

Con la finalidad de dar al usuario el mayor numero de facilidades para realizar tareas específicas como es el proceso de clasificación, se diseño un módulo que realiza la clasificación por hardware, dando como resultado una "innovación" en sistemas de despliegue de imágenes. Un diagrama a bloques del clasificador se muestra en la Figura 9.

CLASIFICADOR

FIGURA 9

El módulo de clasificación se diseñó en base a circuitos comparadores de alta velocidad, esto es con la finalidad de que al tiempo en que la imagen se despliega se realice una comparación entre la información contenida en los ocho registros del módulo de clasificación, y el pixel que se despliega.

#### FUNCIONAMIENTO.

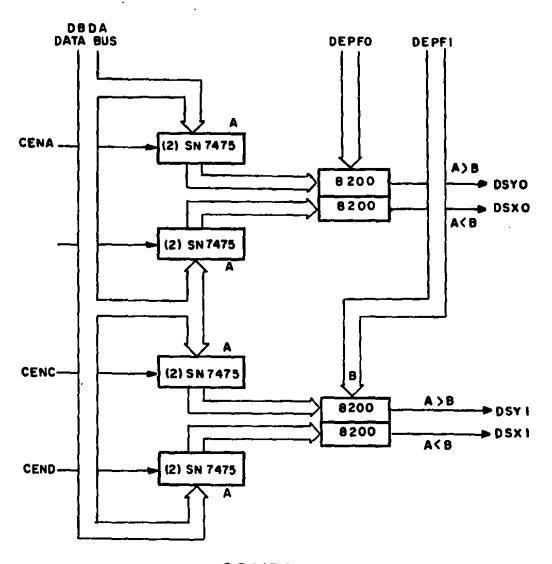

Esta tarjeta tiene como finalidad la de almacenar los limites de comparación (superior e inferior) de dos bandas, por lo que es necesario contar con dos tarjetas para realizar el proceso de clasificación sobre las cuatro bandas. Ver Figura 10.

A la tarjeta del comparador arriban tres buses: bus de datos del sistema de cómputo (DBDA) y los provenientes de dos de las bandas de color (DEPFO-DEPF1).

La carga de los límites de comparación la realiza la unidad de control direccionando cada uno de los registros seleccionados por el usuario con ayuda de las líneas de control CENA, CENB, CENC y CEND. El dato almacenado es proporcionado por medio del bus de datos primero el límite inferior y después el límite superior en forma secuencial para cada una de las bandas.

Los comparadores se encuentran normalmente habilitados para realizar la comparación entre el contenido de los registros de los limites superior e inferior y el bus de la banda correspondiente, obteniendo como resultado cuatro líneas

COMPARADOR

FIGURA 10

(DSYO, DSYI, DSXO y DSX1) en las cuales está representado el resultado de la clasificación de cada uno de los pixels. En dichas señales se encuentra representado, si el pixel al cual se le realizó la clasificación se encuentra dentro o fuera del intervalo (O = fuera del intervalo, 1 = en el intervalo) determinado por los límites inferior y superior de cada una de las bandas, para que posteriormente este resultado sea almacenado en la memoria de bit de gráfica.

Mediante el módulo de control se puede seleccionar en que bit de gráfica se almacena el resultado del proceso de clasificación de una imagen. El módulo de control también puede seleccionar el despliegue antes y después de realizada la clasificación ya que ésta se graba en un plano adicional a la memoria principal.

# 4.3- CURSOR

En los sistemas de despliegue de imágenes, es necesario contar con un dispositivo, mediante el cual se pueda indicar en forma visual sobre el CRT una zona o región de interés para su análisis o estudio. Generalmente estos dispositivos cuando se activan despliegan sobre el monitor una marca de mayor intensidad en forma de cruz o flecha.

A este tipo de dispositivo se le llama Cursor y es de gran utilidad ya que mediante movimientos horizontales y movimientos verticales se puede abarcar toda la información desplegada sobre la pantalla de video.

En el momento en que se ha señalado un pixel por medio del cursor, la información obtenida de éste punto, es colocada

sobre el bus de datos para que posteriormente pueda ser analizada y procesada por el sistema de cómputo.

# FUNCIONAMIENTO.

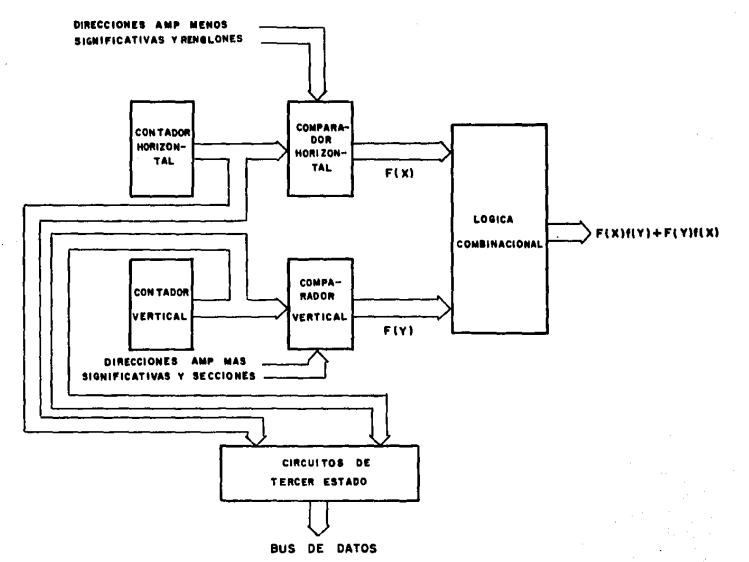

La tarjeta de cursor consta de un banco de contadores, un banco de comparadores, circuitos tercer estado y lógica de control, como se muestra en la Figura 11.

El banco de contadores está implementado con cuatro contadores up/down (cuenta hacia arriba o hacia abajo). Este banco de contadores se dividió en dos para así quedar constituído un banco de contadores horizontales y otro de contadores verticales los que permiten el desplazamiento sobre toda la pantalla de video.

El banco de comparadores está formado por cuatro comparadores de 4 bits cada uno, de igual forma que el banco de contadores, se dividió este banco en dos bloques para así tener los comparadores horizontales y los comparadores verticales.

Los comparadores horizontales reciben las direcciones menos significativas del bus de direcciones de memoria principal (AMF) así como los renglones, y las comparan con las direcciones provenientes de los contadores horizontales, la señal que resulta de esta comparación la denominamos F(x). Cuando F(x) es igual a un uno lógico indica que las direcciones del sistema de despliegue son iguales a las direcciones horizontales.

Por otro lado, los comparadores verticales reciben las direcciones más significativas del bus AMP así como las señales de sección y los comparan con las direcciones provenientes

DIAGRAMA A BLOQUES, TARJETA DEL CURSOR FIGURA 11

de los contadores verticales. La señal resultante de esta comparación la denominamos F(y). Cuando F(y) es igual a un uno lógico indica que las direcciones del sistema de despliegue son iguales a las direcciones verticales. Estas dos señales nos indican un pixel, únicamente, representado por un punto de mayor intensidad sobre el monitor.

Para generar la señal del cursor (una cruz) se utilizaron las señales F(x) y F(y), y por medio de la lógica de

control se implementaron las funciones f(x) y f(y), las cuales indican la posición del pixel con dos pixels adelante y

dos atrás del punto exacto de las comparaciones horizontal y

vertical.

La función F(x) f(y) + F(y) f(x) se implementó con lógica combinacional y mediante ésta es posible desplegar en el monitor una cruz. El punto central de esta cruz, nos indica precisamente el pixel de interés. La información que se obtiene de los contadores horizontales y verticales, se encuentra presente en las entradas del banco de circuitos de tercer estado, esta información representa la dirección del pixel de interés seleccionado. En el momento en que la unidad de control habilita a los circuitos de tercer estado, la información que se localiza en sus entradas es colocada sobre el bus de datos del microprocesador, para que posteriormente este dispositivo direccione dicha localidad, para efectuar el análisis y procesamiento de la información.

# 4.4- DIGITALIZADOR

El digitalizador es un dispositivo de gran ayuda para el fotointérprete ya que permite adquirir información proveniente de una fotografía, un mapa o una imagen en forma rápida y confiable y al mismo tiempo se puede desplegar dicha información sobre el CRT.

Para el sistema de despliegue de imágenes se diseñó un digitalizador en base a un convertidor A/D de video , este circuito es la interfase entre la cámara de televisión y el sistema de despliegue, y nos permite obtener tiempos de conversión de 125 n segundos con 8 bits +/- 1 bit de precisión.

La señal proporcionada por la cámara de televisión es analógica y con la característica de ser una señal normalizada para video, es decir, junto con la información de video se encuentran las señales de sincronia. Por lo tanto, el convertidor análogo/digital tiene que estar sincronizado con la cámara de televisión y el sistema de despliegue.

# FUNCIONAMIENTO.

El digitalizador se activa por medio de la palabra de control, una vez que se ha habilitado pone en estado de espera a la microcomputadora, liberando los buses de direcciones, de datos y de control. En ese momento el control del sistema funciona como un DMA (Direct Memory Access), es decir los buses se encuentran en estado de alta impedancia para que otro dispositivo tome su control.

Para lograr que el microprocesador entre al estado de espera se dispone de un interruptor en el panel de control el

cual inhibe al CPU. Mediante la palabra de control se ordena

la operación de digitalización, en este modo los circuitos

convertidores se activan y empiezan a digitalizar la información que se localiza a su entrada. Esta función está

controlada por la señal CONVERT la cual tiene una frecuencia

de operación de 16 MHz que se obtiene del reloj general del

sistema.

Una vez que empieza el proceso de digitalización la imagen se despliega en el monitor (CRT), y ésta quedará almacenada siempre y cuando el sistema de despliegue y la cámara de televisión se encuentran en sincronia.

Para lograr la sincronía, en el panel de control se localiza un interruptor, que activa la lógica para detectar el pulso de "FILE INDEX". Este pulso indica el momento en que está presente un cuadro par. La digitalización se realiza por renglones y dura exactamente el período correspondiente a un pulso de sincronía vertical, por lo tanto para realizar la digitalización de una imagen se requiere de ocho cuadros de despliegue.

#### CAPITULO U

# INTERFASE Y CONTROL

La unidad de interfase y control se encarga de generar las diferentes señales que se utilizan para la interconexión entre el sistema de despliegue y la microcomputadora.

Dichas señales se pueden englobar en tres (buses) de acuer do a su función para así obtener el Bus de Dirección, Datos y Control.

La unidad de control genera las señales que se requieren, para que el sistema de despliegue realice una función especifica. Dichas funciones son determinadas por la palabra de control. Por medio de ésta el fotointérprete selecciona una de las diferentes actividades que puede realizar el sistema de despliegue, ya se trate de una digitalización, clasificación, manejo de cursor, paso por las memorias auxiliares o dispositivos auxiliares. De acuerdo a la actividad seleccionada el control habilita y genera las señales necesarias para el módulo involucrado.

En la unidad de control también se generan las señales requeridas para el despliegue de la información sobre el CRT.

La unidad de interfase y control está constituída por los siguientes módulos:

Selector de Memoria Principal

Selector de Bit de Gráfica

Selector Vertical

Interfase

Palabra de Control

Convertidor Digital/Analógico

# 5.1- SELECTOR DE MEMORIA PRINCIPAL

La tarjeta selector de memoria principal es la encargada de efectuar el direccionamiento tanto a la memoria principal como a la memoria de bit de gráfica.

Existen dos modos de operación del selector de memoria principal: cuando el sistema de cómputo realiza un acceso a memoria para efectúar una lectura o escritura de datos; y cuando el sistema de despliegue accesa a la memoria en forma de lectura para desplegar la información sobre el CRT.

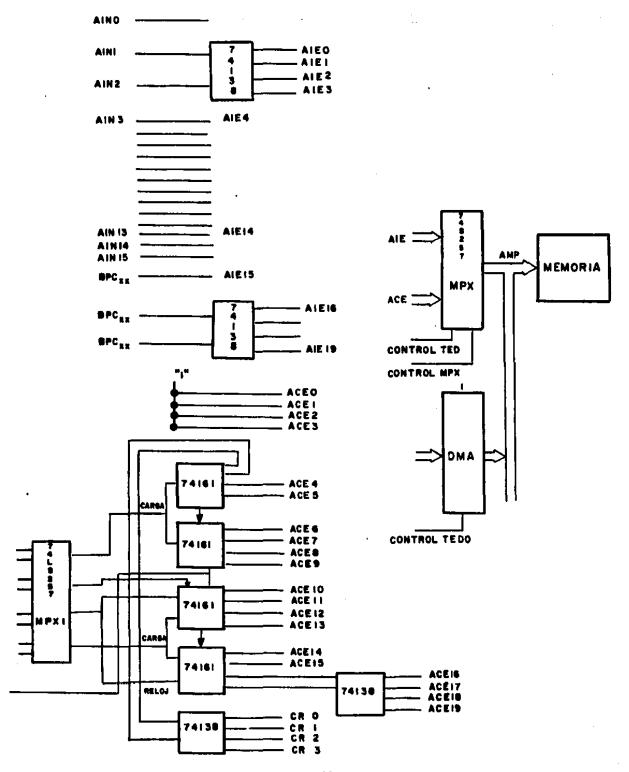

La tarjeta de selector vertical consta de un multiplexor, dos selectores de linea y un contador como se muestra en la Figura 12. Esta tarjeta tiene como entradas las señales del control general, las direcciones de la interfase de entrada y algunos bits de la palabra de control.

La salida de esta tarjeta es el bus de Direcciones de Memoria Principal (AMP), en el cual se tiene lógica de tres estados para poder realizar funciones de Acceso Directo a Memoria (DMA).

# FUNCIONAMIENTO.

El sistema de cómputo de la configuración actual es un microprocesador INTEL 8080 con capacidad de direccionamiento hasta 64 K palabras, por tal razón fue necesario crear una "ventana" de 16 K palabras utilizando los bits (A14 Y A15 = 1), de esta manera el sistema de cómputo ve a la memoria principal del sistema de despliegue como parte de su propia memoria.

La tarjeta de selector de memoria principal es básicamente

FIGURA 12

un multiplexor que tiene dos vectores de información en su entrada. El vector AIE (Dirección de Interfase a la Entrada), determina el modo de acceso del sistema de cómputo a la memoria principal y el vector ACE (Dirección del Contador a la Entrada) permite que la memoria sea leida secuencialmente para tener el despliegue de la imagen almacenada.

El vector AIE está generado en parte por los bits de la interfase de entrada y en parte por algunos bits de la palabra de control. Los cuatro bits menos significativos de AIE son generados con ayuda de un selector de linea (74138) que opera con las combinaciones de los dos bits menos significativos de la interfase con el sistema de cómputo. Los cuatro bits más significativos de AIE son los que indican que sección de memoria puede ser accesada por el sistema de cómputo, estos bits se generan por medio de un selector de línea (74138) que trabaja con la combinación de los dos bits de la palabra de control.

El vector ACE determina las localidades de memoria principal que son accesadas para su despliegue. Los cuatro primeros bits de ACE están habilitados (1 lógico) e indican que existen cuatro renglones direccionados al mismo tiempo. Los bits ACE4-ACE15 indican las direcciones físicas de la memoria principal, estas señales son generadas con un contador implementado con circuitos contadores sincronos de 4 bits (SN74161) conectados en cascada. Los bits más significativos de ACE (ACE16-ACE19) determinan la sección que se está desplegando, estos cuatro bits son generados con un selector de linea (74138) que opera con la combinación de los dos bits más significativos del contador.

Los vectores ACE y AIE se encuentran a la entrada de un multiplexomultiplexor implementado circuitos con res/selectores de datos de 2 a 1 (74257) trabajando en paralelo. Este multiplexor normalmente apunta hacia el bus ACE que nos permite un direccionamiento secuencial sobre banco de memoria principal para el despliegue de información. Cuando se indica que la operación la realizar es un acceso de la microcomputadora, el control genera la señal de MRAC con la cual el multiplexor seleccionará el bus de direcciones provenientes de la interfase de entrada. Este tipo de multiplexores cuenta con lógica de tres estados, lo que nos permite dejar el bus de direcciones "libre" para poder accesar a la memoria con DMA.

# 5.2- SELECTOR DE BIT DE GRAFICA

Esta tarjeta permite la selección de la memoria de bit qráfica, mediante dos formas diferentes de direccionamiento:

- Direccionamiento en paralelo con la memoria principal.

- 2) Direccionamiento atrasado con respecto al de memoria principal.

La primera se utiliza para el modo de operación normal del sistema de despliegue y permite tener longitudes de palabra de ocho bits; la segunda solamente se emplea cuando se clasifica información.

# FUNCIONAMIENTO.

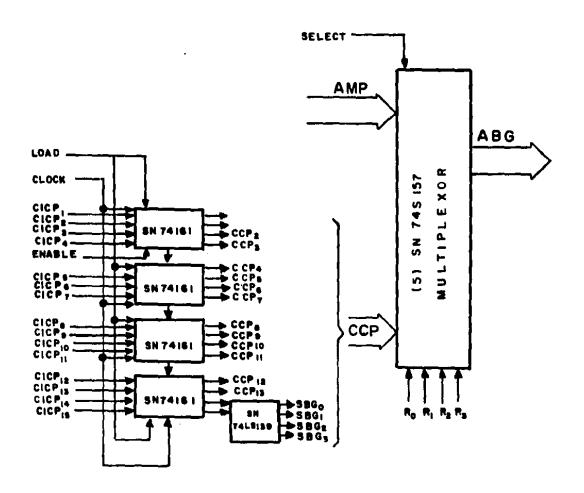

Básicamente la tarjeta selector de bits de gráficas funciona como un multiplexor entre dos vectores digitales, uno procedente del selector de memoria principal AMP (Dirección de Memoria Principal) y el otro vector generado internamente en la tarjeta por un contador programable CCP (Cuenta Contador Programable), como se muestra en la Figura 13.

El contador programable se encuentra implementado con un arreglo de circuitos contadores sincronos de 4 bits (74161) trabajando en cascada. La combinación de los dos primeros bits del contador programable determinan el rengión de la memoria de bit de gráficas en donde se clasifica. Estas señales de dirección son controladas externamente por el control general que fija el rengión donde se está clasificando. En el vector CCP se tienen las direcciones para la memoria de bit de gráfica de CCP2-CCP13. La combinación de los dos bits más significativos del contador programable (74161) a través de selector de linea (74139) genera las señales de sección donde se realiza la clasificación (SBGO, SBG1, SBG2, SBG3).

Los vectores AMP y CCP se encuentran a la entrada de un multiplexor implementado con circuitos multiplexores/selectores de datos de 2 a 1 (74157), los cuales trabajan en paralelo, obteniendo así un multiplexor de 20 líneas de salida las cuales forman el vector de direcciones para la memoria de bit de gráfica ABG (Direcciones de Bit de Gráfica).

Este multiplexor apunta normalmente al bus de direcciones de memoria principal, es decir se encuentra trabajando en paralelo para obtener una palabra de 8 bits de información. Si la operación a realizar es una clasificación, el control ge-

# SELECTOR DE BITS DE GRAFICA

FIGURA 13

neral del sistema proporciona la señal CLASIFICA la cual produce que el multiplexor apunte al bus de direcciones generado por el contador programable (CCP) para determinar exactamente sobre cual bit de gráfica se almacenará el resultado de la clasificación.

# 5.3- CONTROL

La unidad de control se encuentra distribuida en dos tarjetas de circuito impreso: la tarjeta de Control y la tarjeta

de Selector Vertical. Debido a las características requeridas

de velocidado, estas tarjetas contienen solamente circuitos

integrados fabricados en tecnología Schotky.

La unidad de control cumple con las siguientes funciones:

# GENERACION DE SENALES DE CONTROL.

A partir de un oscilador de 16 MHz se producen ocho fases, las que combinadas en forma lógica dan los tiempos de acceso a las diversas memorias. Las señales de lectura/escritura así obtenidas, permiten la lectura dinámica de la memoria para el despliegue continuo de la información en el monitor policromático.

# SINCRONIZACION.

La unidad de control proporciona los tiempos precisos de acceso a las memorias y se encarga de sincronizar las diversas funciones del sistema, para evitar la pérdida de sincronia entre el generador de video y el sistema digital.

#### INTERFASE.

La unidad de control funciona además como interfase para satisfacer los requerimientos de lectura/escritura del sistema de cómputo sin interrumpir por esto el despliegue de la imagen almacenada. Con tal fin la unidad de control produce una lectura de memoria equivalente a cuatro pixels, dicha información es almacenada en los registros de salida, para posteriormente ser desplegados de acuerdo a la selección de cada uno de estos registros, permitiendo así, un acceso del procesador cada 350 nseg. entre lectura y lectura.

# SELECCION DE MODOS DE OPERACION.

La unidad de control verifica periódicamente el modo de operación seleccionado por el usuario, de tal manera que genera las señales de control y enruta la información (pixels) hacia las memorias y dispositivos auxiliares.

# FUNCIONAMIENTO.

La generación de las señales de control se realizan a partir del contador programable (74161A6) el cual se encuen tra operando con la señal de reloj lo cual tiene una frecuen cia de 16 MHZ.

Las salidas de dicho contador se encuentran disponibles a la entrada del circuito selector de linea (74139A5). Este circuito se encarga de generar las fases ( 1, 2, 3, 4) utilizando para ello los bits más significativos del contador, así mismo genera las subfases ( 1, 2, 3, 4) tomando los bits menos significativos de dicho contador.

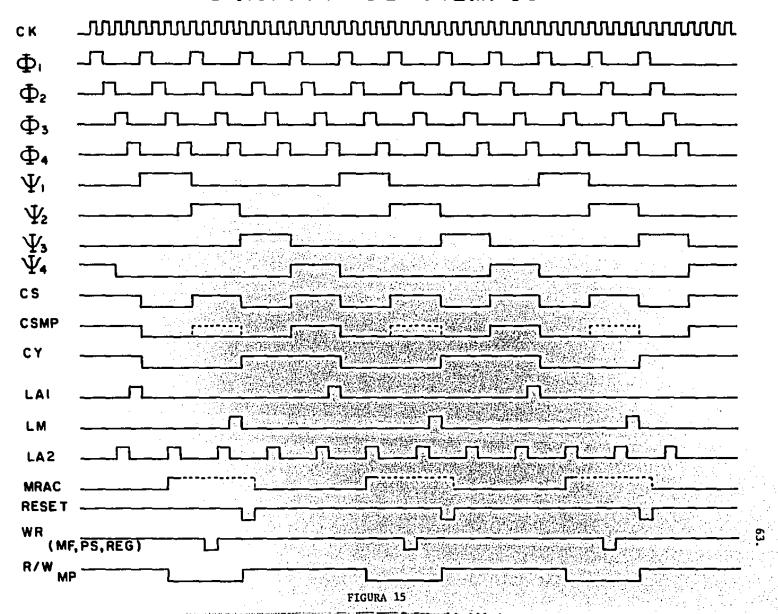

# DIAGRAMA DE TIEMPOS

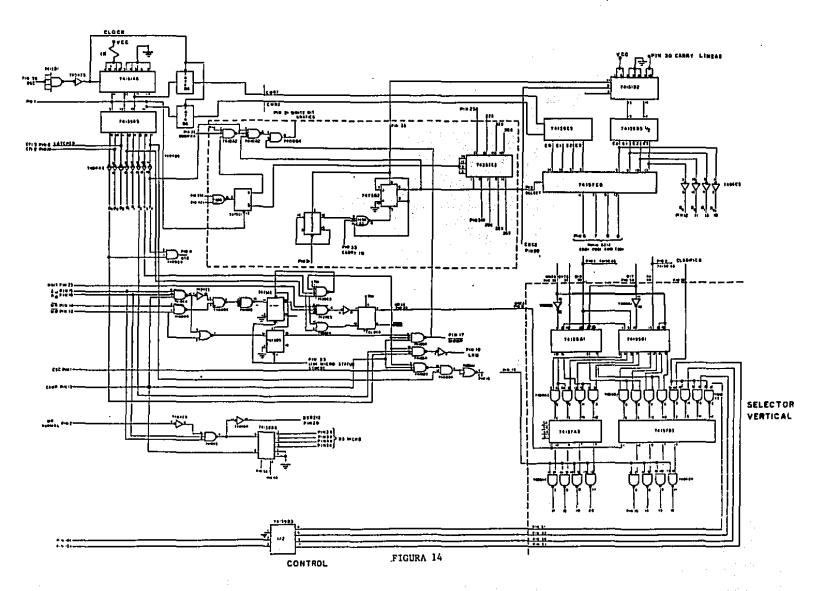

En la figura 14 se muestra el diagrama de la tarjeta de control. La figura 15 muestra el diagrama de tiempos que se obtienen de la tarjeta de control.

Estas fases controlan tanto la generación de las señales Chip Select como la sincronia de las señales que se utilizan para la interfase con el sistema de cómputo.

Cuando se presenta la conjunción A14 . A15 = 1 el sistema reconoce que existe una petición de acceso de lectura o escritura a memoria. Para determinar si dicho acceso será a memoria principal o a registros se realiza una verificación del estado de interruptor correspondiente a registros (1 = Memoria Principal, O = Registros), esta verificación se lleva a cabo en la compuerta nand de 3 entradas (7410C4).

Si se trata de un acceso a memoria principal, se detecta el tipo de operación que se llevará a cabo (lectura o escritura), por medio de la compuerta nand (7400D4).

Ciclo de Escritura. Si se trata de una operación de escritura, el flip-flop (7473B3) (utilizando como reloj la se fal de "STATUS-STROBE" del sistema de cómputo), almacena la petición para generar una escritura, y la mantiene presente mientras el flip-flop (7473A3), indica al microprocesador que debe realizar un ciclo de espera para estar en sincronia. Esto produce que el microprocesador conteste con la señal de "WAIT" que se localiza a la entrada de la compuerta nand de 4 entradas (7420C3), al presentarse la fase 1, el flip-flop (7473) genera la señal de "memory request acknowledge" (MRAC).

La señal de MRAC es utilizada para controlar las siguien-

tes actividades del sistema de despliegue:

-La apertura del multiplexor contenido en la tarjeta del Selector de Memoria Principal, para permitir el paso de las direcciones del sistema de cómputo.

-La generación de la señal de lectura/escritura para los bancos de memoria príncipal y bit de gráfica.

-El paso de la señal de chip select intermedio, el cual es generado por la fase. A por medio de la lógica combinacional implementada con circuitos nand, and y or respectivamente (741003, 740804 740261). Esta señal es utilizada por el módulo de Selector Vertical, el cual se encarga de generar los chip select "intermedios" para todos aquellos módulos de memoria principal o bit de gráfica seleccionados.

Ciclo de Lectura. — En caso de que la operación sea una lectura de memoria, la señal de "Memory Read" (MR) del microproce sador junto con la condición A14 . A15 = 1 y a través de la compuerta nand (7410D3) habilita al selector de linea (7413BD6). Este circuito es el encargado de producir la señal de "device select" para cada uno de los registros que contienen la información. Al mismo tiempo por medio de un inversor (7404A4), se habilita a todos los registros que apuntan al sistema de cómputo, colocando la información en el Bus de Datos para que sea leida.

Una vez realizada la operación seleccionada, ya sea de lec tura o escritura a memoria, en el circuito inversor (7404A4) se genera en fase con 2 - 4 la señal de "latcheo" (LRM) para los registros (8212) de todas las bandas que apuntan al microprocesador. Al concluir un ciclo (lectura o escritura) es necesario producir un "reset", con lo cual el sistema que-

dará listo para aceptar una nueva petición de acceso, esta señal de "RESET" es producida por la compuerta nand (742003).

Con el fin de generar cuatro fases retardadas, necesarias en el proceso de selección de los registros que apuntan a la memoria de función, se utilizó un contador programable (74161A6), los bits más significativos de este contador son almacenados durante una ciclo de reloj en el "latch" (7474B6). Las salidas de éste son conectadas al selector de línea (74139C5) en donde se forman las fases retardadas EO, E1, E2, E3, dichas fases pasan normalmente a través del multiplexor (74157C6) hacia los registros que controlan la salida de cada pixel.

En caso de pedirse una clasificación y con el objeto de es cribir el resultado de ésta en la dirección del pixel que se está clasificando, se realiza una selección de los renglones para bit de gráfica (RO, R1, R2, R3).

Esta selección se efectúa por medio de las fases E0'-E3', las cuales son generadas a partir un contador programable (74161B2). El funcionamiento de este circuito está controlado por el carry del contador de lineas de video y por la señal de petición de clasificación (CRC2). La señal CRC2 controla el funcionamiento del multiplexor (74157C6), y por medio de esta señal se determinan las fases que habilitan la salida de los registros hacia la memoria de función.

La selección del banco de memoria de bit de gráfica, sobre el cual queda almacenado el resultado de la clasificación, se realiza por medio de los interruptores SB1 y SB2 los cuales controlan al selector de linea (74139D5) y por medio de éste habilita el chip select apropiado.

# 5.4- SELECTOR VERTICAL

La Tarjeta de Selector Vertical contiene todos los elementos necesarios para controlar la selección de las diferentes

memorias así como la lógica necesarias para efectuar el proceso de clasificación.

Una de las características en el diseño era la de poder seleccionar en que banda se realizaria la escritura, por ejemplo cuando se digitaliza una imagen, o bien cuando se desea escribir desde el microsistema solamente una banda (7 bits) o bien una banda y su bit de gráfica (8 bits) o en alquinos casos escribir únicamente el bit de gráfica (1 bit).

Por otra parte, se previó la posibilidad de escribir y leer palabras de dos bandas (14 bits) o bien dos bandas y sus bits de gráficas (16 bits), esto se hizo ya que se desconocía las características exactas del sistema de cómputo al cual se conectaría el sistema de despliegue de imágenes.

# FUNCIONAMIENTO.

La operación del módulo selector vertical es determinada por la palabra de control. Por medio de ésta el fotointér-r prete puede seleccionar las diferentes memorias que se desean accesar. Para realizar este proceso de selección en la unidad de control se dispone de tres interruptores llamados: bit, byte y word y dependiendo del estado en que se encuentren dichos interruptores (°1° lógico = habilitado, °0° lógico = deshabilitado), será la longitud de la información accesada, (bit de gráfica, 1 banda con/sin bit de gráfica, 2 bandas

The second secon

con/sin bit de gráfica). La señal (nivel lógico) proporcionada por los interruptores bit, byte y word se localiza a la entrada de los circuitos decodificadores (74155A1, 74155B1), las salidas de estos circuitos son utilizadas por el arreglo de compuertas nand (7400A2, 7400B2, 7400C2), mediante las cuales es posible la generación de las señales de CHIP'S SE LECT tanto para la memoria principal como para la memoria de bit de gráfica.

Si la operación a efectuar es una digitalización, el cir cuito multiplexor (74157A3) apunta a los interruptores (SR, SV, SA) para seleccionar la banda correspondiente a la digitalización.

En caso contrario, permite el paso de las señales de control que afectarán a la compuerta nand (7400A4) en donde la señal de CHIP SELECT de despliegue, lectura/escritura se distribuye para las diferentes bandas.

Las señales para las memorias de bit de gráfica se generan a través del circuito multiplexor (74157B3), el cual es controlado únicamente por la señal de petición de acceso a memoria MRAC. Esta señal permite el paso de las líneas de control hacia las compuertas NAND (7400B4) en donde se generan los CHIP SELECTS correspondientes a cada una de las bandas: Así mismo, por medio de la selección manual se controla el paso de las líneas junto con la señal de clasifica proveniente de los circuitos (7400C2) y el (74139D5) de la tarjeta de control.

El resultado de una clasificación independientemente de que haya petición o no, se está almacenando en el 'latch' (7475Ci) teniendo en su entrada un circuito NAND (743OD1) de ocho entradas provenientes de las tarjetas de clasificación.

- El flip-flop (7473B2) forma el candado necesario para realizar las siguientes actividades:

- 10. Permitir el paso de las fases EO', E1', E2', E3', durante cuatro pantallas.

- 20. Colocar el resultado de la clasificación sobre el bus de datos de las memorias de bit de gráfica esto se realiza a través del circuito multiplexor (74257C2).

El candado se libera al concluirse la cuenta de cuatro pantallas, esto se logra aplicando al reset del flip-flop (7473B2) el bit de cuenta proveniente de la tarjeta de control.

El candado tiene como condición de entrada del carry del contador de lineas, de tal manera que se logra la sincronta con el principio de un despliegue, para esto el circuito nad de 3 entradas (7410A2) proporciona la señal de reloj para el flip-flop (7473B2).

El proceso de clasificación puede constar de varias clasificaciones y en ocasiones algunas de éstas no es de interés el almacenarlas, por lo que resulta necesario tener un control que permita elegir si existe modificación o no sobre la los datos. Haciendo uso del interruptor modifica puede inhibirse o activarse la generación de la señal de escritura de bit de gráfica, los circuitos que nos permiten realizar esta actividad son la compuerta nand (7410A2) y la compuerta nand (7408B4) teniendo como entrada en este último la señal de escritura a memoria principal MWMP.

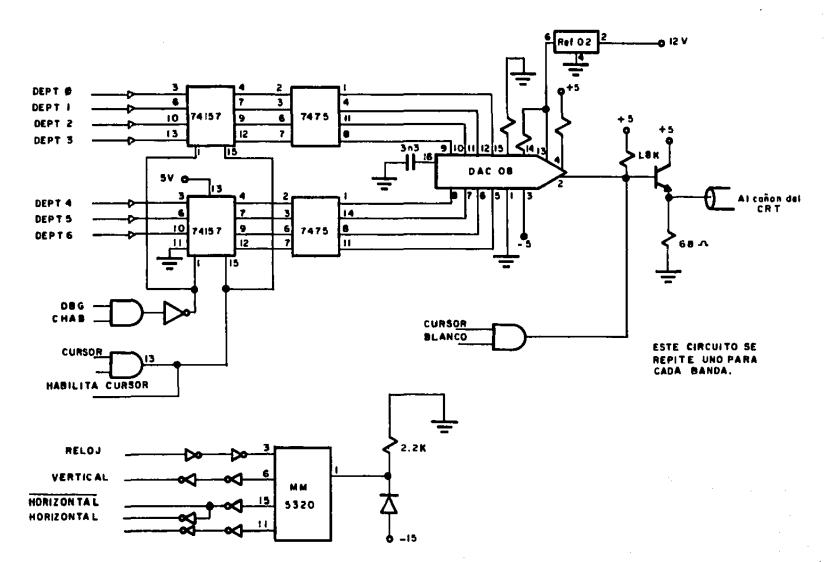

#### 5.5- CONVERTIDOR DIGITAL/ANALOGICO

Los datos provenientes de los bancos de memoria principal y de bit de gráfica son colocados sobre tres buses de 8 bits cada uno llamados DEPFO, DEPF1, DEPF2 que corresponden a las bandas ROJA, AZUL y VERDE.

Esta información es colocada a la entrada del módulo de conversión digital/analógico para su despliegue sobre el monitor de T.V.

La función del módulo convertidor digital/analógico es la de generar las diferentes señales de sincronia para el despliegue de la información, de acuerdo a los requerimientos de las normas de televisión.

Para ello, en este módulo se han instrumentado tres circuitos iguales; uno por banda y un circuito general encargado de sincronizar el video.

El diagrama a bloques del convertidor digital/analógico se muestra en la figura 16.

#### FUNCIONAMIENTO.

Ya que existen diferentes modos de operación del sistema de despliegue, los cuales están intimamente ligados con la etapa de conversión digital/analógica, se implementó sobre esta etapa una lógica de control la cual selecciona el modo de operación de acuerdo a la actividad que se desea realizar.

La información digital obtenida de los diferentes bancos

1

de memoria se localiza a la entrada de un circuito multiplexor, el cual tiene tres formas diferentes de operación: modo normal de despliegue, modo de despliegue de bit de gráfica y modo de despliegue del cursor. Los modos de operación son controlados por la señal que habilita el bit de gráfica y a el cursor.

#### MODO NORMAL DE DESPLIEGUE.

Para asegurar el arribo de la información digital al circuito convertidor D/A, se dispuso, a la salida del multiple-xor, un circuito de almacenamiento temporal (7475). Este circuito presenta la información al convertidor digital analógico (DACOB) para que éste a su vez genere la señal de video para cada uno de los cañones del CRT.

#### MODO DE DESPLIEGUE DE BIT DE GRAFICA.

Si se desea que la información almacenada en la memoria de bit de gráfica sea desplegada, es necesario activar la señal (CHAB) por medio del tablero de control, esta señal junto con el dato proveniente de bit de gráfica hace que el multiplexor apunte a una palabra programada en la tarjeta, correspondiendo al nivel más obscuro en el video, teniéndose en el despliegue la sobreposición de un color intenso donde el bit de gráfica es cierto.

#### MODO DE DESPLIEGUE DEL CURSOR.

Si se desea que la señal proporcionada por la tarjeta del cursor (cruz) sea desplegada sobre el CRT, es necesario ac-tivar la señal habilita cursor a través del interruptor que

se localiza en el tablero de control del sistema.

La señal habilita cursor provocará que los multiplexores a los cuales arriba la información, generen una salida de mayor intensidad, dicha señal corresponde a la saturación de los cañones, lo cual provoca que se despliegue una "cruz" (señal del cursor) en el nivel del blanco.

Para establecer la sincronía de cada uno de los módulos constitutivos del sistema, así como del monitor de T.V., se utilizó un circuito generador de sincronía (MM5320) al que se proporciona como entrada el reloj general del sistema (16 MHz). Este circuito se encarga de generar las señales de sincronía horizontal, vertical, blanco y principio de campo, mismas que cumplen con las normas de televisión. Dichas señales a su vez interaccionan con el control del sistema de despliegue para lograr la sincronía de la etapa digital y de video.

#### 5.6- PALABRA DE CONTROL

La palabra de control ha sido diseñada para brindar todas las facilidades necesarias al usuario en el despliegue interactivo de imagenes multiespectrales.

- La palabra de control tiene las siguientes funciones:

- a).-Facilitar la escritura/lectura a las diferentes me morias del sistema de despliegue.

- b).-Selección y control del modo de despliegue durante una aplicación dada tanto programática (software) co mo manual (hardware).

c).-Controlar la utilización de dispositivos externos.

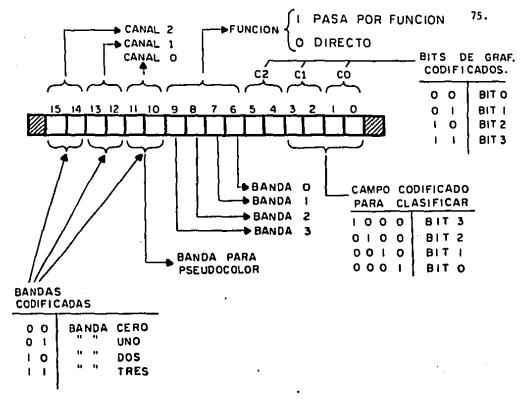

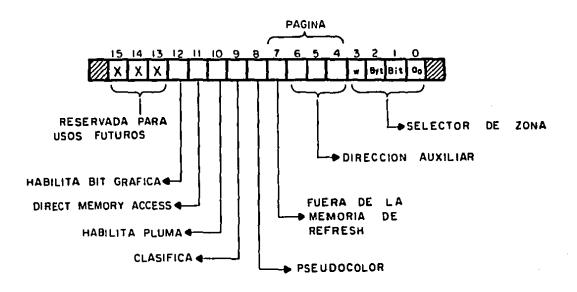

La palabra de control consta de 32 bits, dividida en dos subpalabras de 16 bits c/u con los siguientes formatos; como se muestra en la figura 17.